- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

I'm investigating DVFS on an IMX53 based platform running Linux. We are using the Freescale Android 10.2 BSP

Both frequency and voltage scaling appear to be enabled - as shown below:

cat /sys/devices/platform/mxc_dvfs_core.0/enable

DVFS is enabled

However when I look at the min and max frequencies I see the following

cat /sys/devices/system/cpu/cpu0/cpufreq/cpuinfo_max_freq

800000

cat /sys/devices/system/cpu/cpu0/cpufreq/cpuinfo_min_freq

800000

This suggests that only one frequency is used and so no scaling is taking place.

Is this correct? If so how can I change this?

Thanks,

Bruno

已解决! 转到解答。

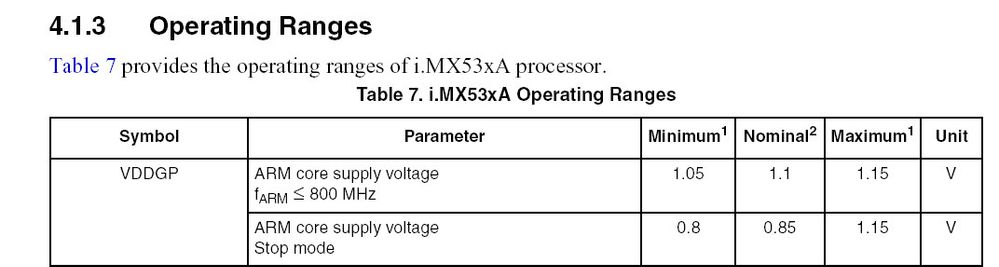

Hi Bruno

it can at lower frequencies without changing

core voltage. It hasn't been characterised for operation with lower

core voltages running at lower frequencies.

~igor

Hi Bruno

sect.20.2 Software Operation attached document

shows how to enable DVFS.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Igor,

I have seen this and DVFS is enabled as described in the document.

However the issue is that the min and max frequencies as shown by the proc file system are the same which suggests no frequency scaling can take place.

The min and max values seem to derive from a table in the file kernel_imx/arch/arm/mach-mx5/mx53_wp.c. There are a number of structures ( dvfs_wp and cpu_wp ) that seem to have a bearing on this but I have not been able to find a description of their usage. I've included the relevant ones that are being used for our board.

/* Place holder for dvfs_core setpoints for AEC parts */

static struct dvfs_wp dvfs_core_setpoint_aec[] = {

{33, 0, 33, 10, 10, 0x08} }; /*800MHz*/

/* working point for auto */

static struct cpu_wp cpu_wp_aec[] = {

{

.pll_rate = 800000000,

.cpu_rate = 800000000,

.pdf = 0,

.mfi = 8,

.mfd = 2,

.mfn = 1,

.cpu_podf = 0,

.cpu_voltage = 1100000,},

};

So can frequency scaling take place if the min and max frequency are the same? Is this determined by the structures shown above and, if so, how should these structures be used?

Thanks,

Bruno

Hi Bruno

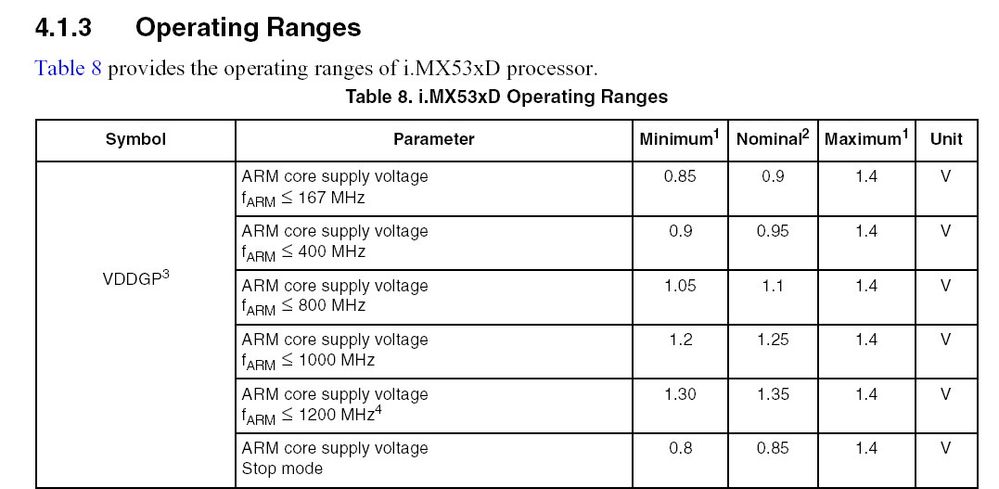

had board followed i.MX53 SMD design and has PMIC ?

Also could you try with linux

L2.6.35_11.05_ER_SOURCE : Linux 2.6.35 Source Code Files

and documentation 11.05 for i.MX53 SABRE Tablet.

~igor