- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm investigating DVFS on an IMX53 based platform running Linux. We are using the Freescale Android 10.2 BSP

Both frequency and voltage scaling appear to be enabled - as shown below:

cat /sys/devices/platform/mxc_dvfs_core.0/enable

DVFS is enabled

However when I look at the min and max frequencies I see the following

cat /sys/devices/system/cpu/cpu0/cpufreq/cpuinfo_max_freq

800000

cat /sys/devices/system/cpu/cpu0/cpufreq/cpuinfo_min_freq

800000

This suggests that only one frequency is used and so no scaling is taking place.

Is this correct? If so how can I change this?

Thanks,

Bruno

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Bruno

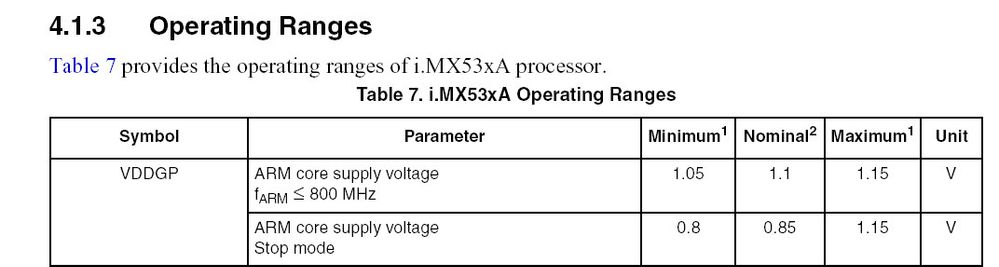

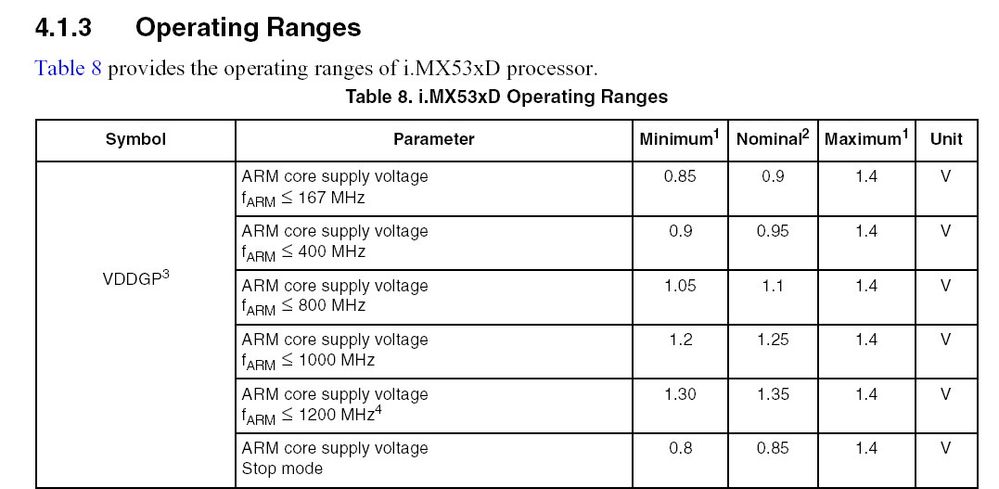

it can at lower frequencies without changing

core voltage. It hasn't been characterised for operation with lower

core voltages running at lower frequencies.

~igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Bruno

sect.20.2 Software Operation attached document

shows how to enable DVFS.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

I have seen this and DVFS is enabled as described in the document.

However the issue is that the min and max frequencies as shown by the proc file system are the same which suggests no frequency scaling can take place.

The min and max values seem to derive from a table in the file kernel_imx/arch/arm/mach-mx5/mx53_wp.c. There are a number of structures ( dvfs_wp and cpu_wp ) that seem to have a bearing on this but I have not been able to find a description of their usage. I've included the relevant ones that are being used for our board.

/* Place holder for dvfs_core setpoints for AEC parts */

static struct dvfs_wp dvfs_core_setpoint_aec[] = {

{33, 0, 33, 10, 10, 0x08} }; /*800MHz*/

/* working point for auto */

static struct cpu_wp cpu_wp_aec[] = {

{

.pll_rate = 800000000,

.cpu_rate = 800000000,

.pdf = 0,

.mfi = 8,

.mfd = 2,

.mfn = 1,

.cpu_podf = 0,

.cpu_voltage = 1100000,},

};

So can frequency scaling take place if the min and max frequency are the same? Is this determined by the structures shown above and, if so, how should these structures be used?

Thanks,

Bruno

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Bruno

had board followed i.MX53 SMD design and has PMIC ?

Also could you try with linux

L2.6.35_11.05_ER_SOURCE : Linux 2.6.35 Source Code Files

and documentation 11.05 for i.MX53 SABRE Tablet.

~igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

We have followed the mx53_ard design and we do have a PMIC (LTC3589) . Is there something different in the mx53_smd design regarding DVFS that we should be following?

Thanks,

Bruno

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

But is there any reason why we can't use frequencies lower than 800MHz?

Thanks,

Bruno

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Bruno

automotive parts were not characterized for these

frequencies.

~igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

800Mz. is the maximum frequency of the AEC part. So it can run at lower frequencies. It just hasn't been characterised at these lower frequencies. Is this correct?

Bruno

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Bruno

it can at lower frequencies without changing

core voltage. It hasn't been characterised for operation with lower

core voltages running at lower frequencies.

~igor