- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

MIPI Camera Frame corruption in IMX8MM when MIPI_DOUBLE_CMPNT and MIPI_YU_SWAP is enabled in CSI_CSICR18

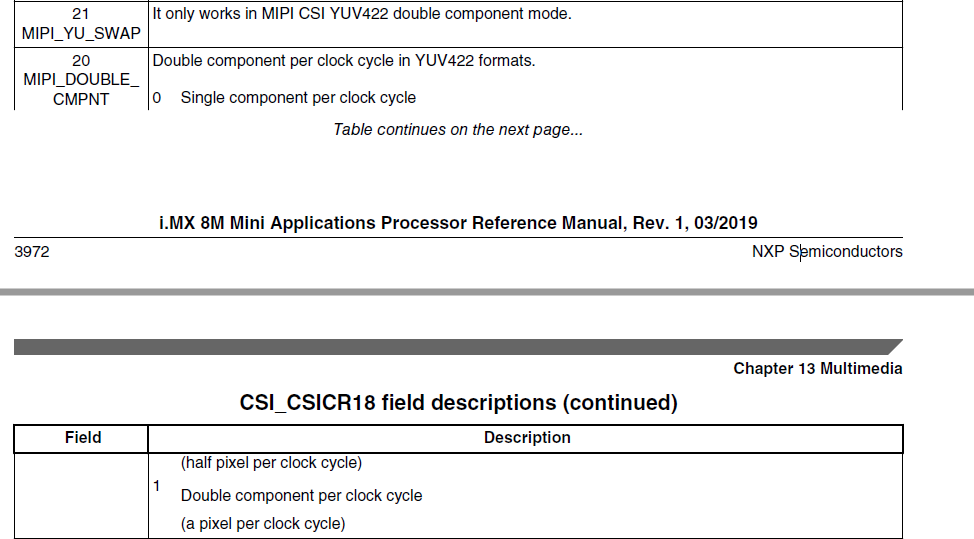

MIPI Camera frame corruption occurs in IMX8MM when MIPI_DOUBLE_CMPNT and MIPI_YU_SWAP is enabled in CSI_CSICR18 (CSI Control Register 18).

The same works in IMX8M.

I know that the MIPI CSI drivers are different for IMX8M and IMX8MM. Is there something that has to be done in addition, in MIPI CSI driver of IMX8MM to mimic the same behaviour as IMX8M? gogoer

已解决! 转到解答。

Hi Ashwanth:

Any way I will sync this issue internally.

Before get result please try below patch for you issue. This patch is based on 4.14.98 GA 2.0

diff --git a/drivers/media/platform/mxc/capture/mxc_mipi_csi.c b/drivers/media/platform/mxc/capture/mxc_mipi_csi.c

index a7964b7b8345..5b4fec5dd9b3 100644

--- a/drivers/media/platform/mxc/capture/mxc_mipi_csi.c

+++ b/drivers/media/platform/mxc/capture/mxc_mipi_csi.c

@@ -488,6 +488,8 @@ static void __mipi_csis_set_format(struct csi_state *state)

val = (val & ~MIPI_CSIS_ISPCFG_FMT_MASK) | state->csis_fmt->fmt_reg;

mipi_csis_write(state, MIPI_CSIS_ISPCONFIG_CH0, val);

+ pr_info("fmt: %#x, %d x %d; CONFIG:0x%x \n", mf->code, mf->width, mf->height, val);

+

/* Pixel resolution */

val = mf->width | (mf->height << 16);

mipi_csis_write(state, MIPI_CSIS_ISPRESOL_CH0, val);

@@ -522,8 +524,11 @@ static void mipi_csis_set_params(struct csi_state *state)

val |= MIPI_CSIS_ISPCFG_ALIGN_32BIT;

else /* Normal output */

val &= ~MIPI_CSIS_ISPCFG_ALIGN_32BIT;

+ val |= 1 << 12;

mipi_csis_write(state, MIPI_CSIS_ISPCONFIG_CH0, val);

+ pr_info(" mipi_csis_set_params CONFIG:0x%x\n", val);

+

val = (0 << MIPI_CSIS_ISPSYNC_HSYNC_LINTV_OFFSET) |

(0 << MIPI_CSIS_ISPSYNC_VSYNC_SINTV_OFFSET) |

(0 << MIPI_CSIS_ISPSYNC_VSYNC_EINTV_OFFSET);I am testing with a 4 lane AR1335 MIPI Camera. The data format of the sensor is UYVY. Since the waylandsink of Gstreamer supports YUYV, I need to swap the bits to avoid using a videoconverter. Since using a videoconverter means a drop in framerate. By enabling the MIPI_DOUBLE_CMPNT and MIPI_YU_SWAP, I was able to stream using wayland sink in IMX8M, but when I tried the same in IMX8MM, frame corruption happens.

Hi Ashwanth:

So far we did not have good way to solve your issue,

But designer has below suggestion:

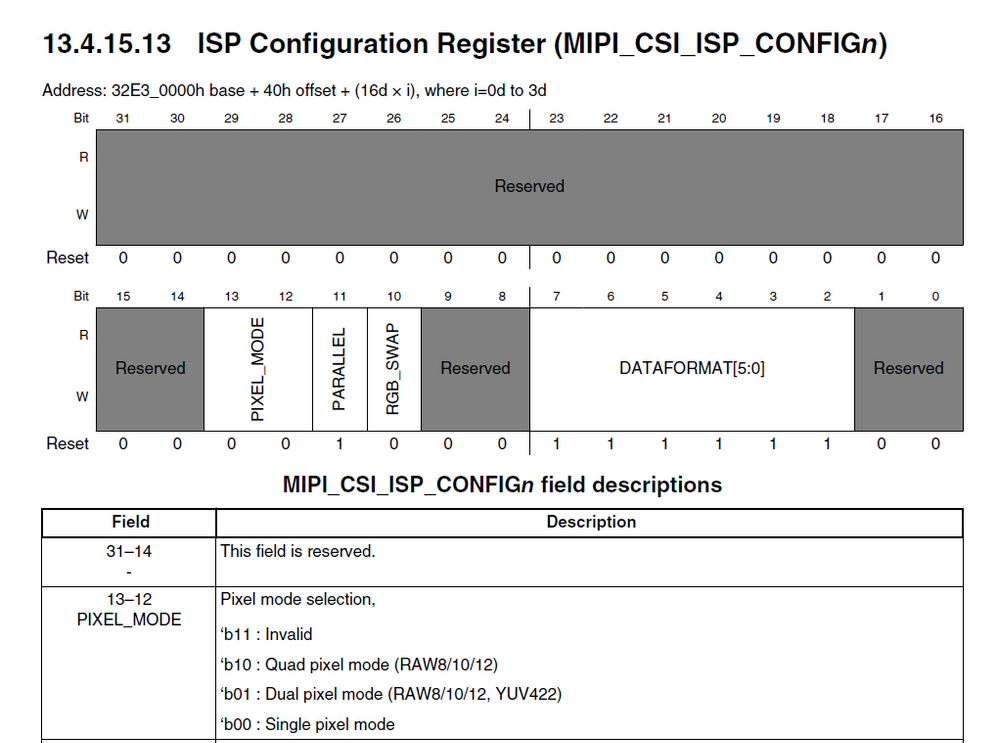

1: confirm camera sensor output double component data:

2: confirm CR18 BIT20/BIT21 MIPI_YU_SWAP/MIPI_DOUBLE_CMPNT be set

3: confirm bit 12/13 of MIPI_CSI_ISP_CONFIG0 PIXEL_MODE is 1

4: Try set /clear CR18 BIT4/BIT5 BASEADDR_SWITCH_EN & BASEADDR_SWITCH_SEL

Hi Ashwanth:

Any way I will sync this issue internally.

Before get result please try below patch for you issue. This patch is based on 4.14.98 GA 2.0

diff --git a/drivers/media/platform/mxc/capture/mxc_mipi_csi.c b/drivers/media/platform/mxc/capture/mxc_mipi_csi.c

index a7964b7b8345..5b4fec5dd9b3 100644

--- a/drivers/media/platform/mxc/capture/mxc_mipi_csi.c

+++ b/drivers/media/platform/mxc/capture/mxc_mipi_csi.c

@@ -488,6 +488,8 @@ static void __mipi_csis_set_format(struct csi_state *state)

val = (val & ~MIPI_CSIS_ISPCFG_FMT_MASK) | state->csis_fmt->fmt_reg;

mipi_csis_write(state, MIPI_CSIS_ISPCONFIG_CH0, val);

+ pr_info("fmt: %#x, %d x %d; CONFIG:0x%x \n", mf->code, mf->width, mf->height, val);

+

/* Pixel resolution */

val = mf->width | (mf->height << 16);

mipi_csis_write(state, MIPI_CSIS_ISPRESOL_CH0, val);

@@ -522,8 +524,11 @@ static void mipi_csis_set_params(struct csi_state *state)

val |= MIPI_CSIS_ISPCFG_ALIGN_32BIT;

else /* Normal output */

val &= ~MIPI_CSIS_ISPCFG_ALIGN_32BIT;

+ val |= 1 << 12;

mipi_csis_write(state, MIPI_CSIS_ISPCONFIG_CH0, val);

+ pr_info(" mipi_csis_set_params CONFIG:0x%x\n", val);

+

val = (0 << MIPI_CSIS_ISPSYNC_HSYNC_LINTV_OFFSET) |

(0 << MIPI_CSIS_ISPSYNC_VSYNC_SINTV_OFFSET) |

(0 << MIPI_CSIS_ISPSYNC_VSYNC_EINTV_OFFSET);