- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

MIPI CSI and IPU configuration (IMX6Q)

Hi there,

I have some questions regarding the set up of the CSI and IPU blocks. Especially how they are set up in the current Linux implementation (kernel 3.14).

I'm trying to receive a MIPI-CSI2 camera input which is transmitting YUV422 (UYVY mode, the only mode specified in CSI2 standard).

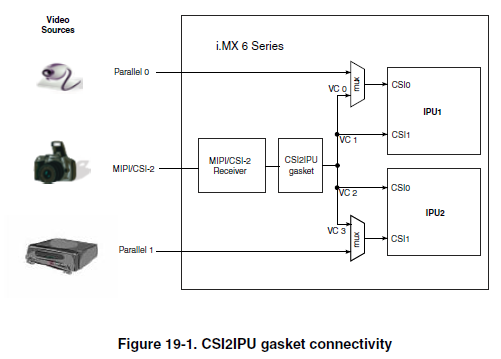

1. CSI2IPU

I can't find any initialisation of this block in the code? Yet as far as I can tell it should be set to UYVY mode and non gated clock mode (iMX6 RM says non gated mode for MIPI but doesn't go into any detail on that).

According to the RM this block is only used for MIPI. Why is the default config YUYV and gated mode and never changed by the Linux drivers (even if MIPI camera is used, such as ov5640_mipi)?

2. IPU SENS_CONF

This register seems to be incorrectly configured for MIPI CSI2 cameras if using the mxc_v4l2_capture module. There is no way the mxc_v4l2_capture can pass IPU_CSI_CLK_MODE_NONGATED_CLK to the ipu_csi_init_interface() function. The only MIPI camera I can find is the ov5650_mipi and when using this clk mode (i.e. PRTCL field of SENS_CONF) is set to 0 (gated clock mode).

What are correct settings for SENS_CONF register for MIPI cameras? Regarding clock mode, and clk, data h/vsync polarity? This must depend on what CSI2PU outputs but it is not well documented.

The issue I'm seeing with my custom MIPI camera is that the IPU seems to miss End Of Frame events. I need to transmit multiple frames for the IPU to store one to memory, and then usually I get a New Frame Before End Of Frame IRQ status. My camera is sending start of frame / end of frame correctly as far as I can tell. I have tried setting the non gated clock mode etc, but it doesn't help. I'm transmitting with a 400 MHz MIPI CSI2 DDR clock with 4 lanes. The IPU is clocked at 270 MHz.

Best regards,

Kristoffer

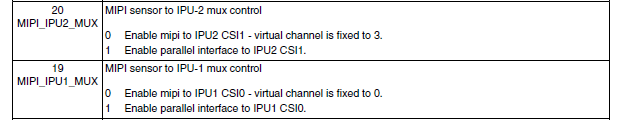

You need to care about which VC is used. Then the CSI ID no. and IPU ID no. are match with the VC number that you used.

Also, the IOMUXC_GPR setting for MIPI.

for example: i.MX6Q , in IOMUXC_GPR1

Yes that is not my problem. The correct CSI and IPU is used.

I'm using a Freescale 3.14.28 kernel. The camera is a custom MIPI camera.

I have got image transfers (YUV422) working at 200 MHz MIPI lane frequency but not at 400 MHz. Nor if I'm using generic data instead of YUV422.

I am interested in getting in touch with someone with detailed knowledge of of the CSI, CSI2IPU and IPU components.