- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- IPU v3 CSI input with FV (Frame Valid) instead of VSYNC in gated clock mode.

IPU v3 CSI input with FV (Frame Valid) instead of VSYNC in gated clock mode.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am using an imx6 to capture data from a parallel Aptina MT9P031 camera via the CSI0 interface in gated clock mode. As per other discussions in this forum, I've modified the Linux Freescale driver to support capturing 16 bit generic data through CSI->MEM.

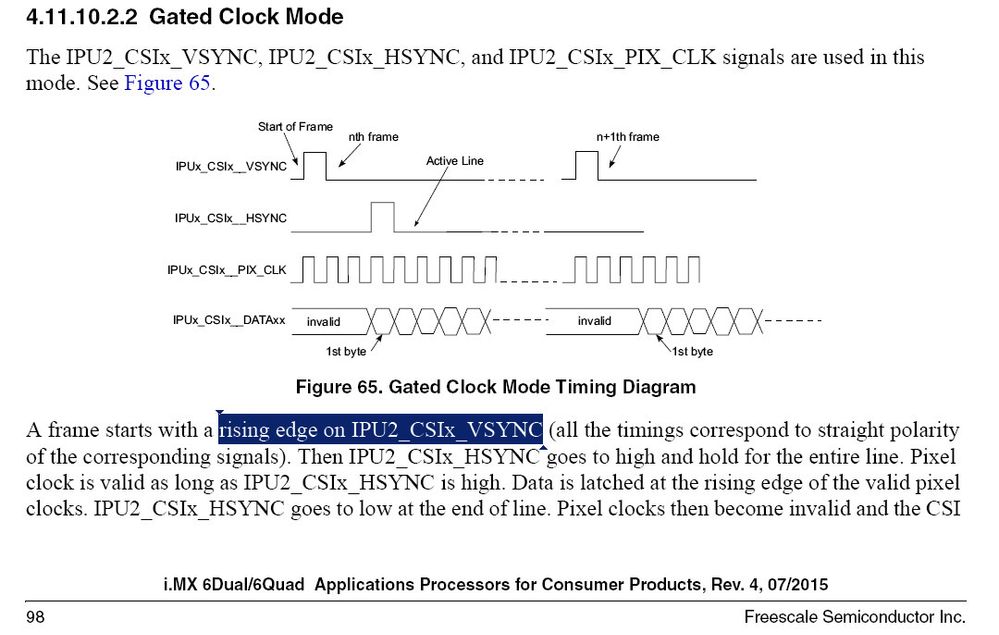

Some captured frames appear to be a combination of two frames indicating a vertical synchronisation issue. The MT9P031 camera uses a Line Valid (LV) signal and Frame Valid (FV) signal instead of a single HSYNC and VSYNC pulse indicating the start of a line/frame. The FV signal remains active through the entire frame transfer and so does not match the timing diagrams shown in the imx6 RM which indicate HSYNC/VSYNC as having a single pulse.

The following thread indicates that for HSYNC, only the leading edge is important to determine the start of a line. IPU v3 CSI0, HSYNC and DATA_EN questions in gated clock mode.

Does the same apply for the VSYNC input? ie Is the VSYNC input treated as an edge triggered or level triggered signal?

If this is a level triggered input, what is the suggested method to connect sensors which utilise line/frame valid signals instead of hsync/vsync inputs?

Thank you

Austin

Message was edited by: Austin Phillips Corrected title to specify frame valid rather than line valid

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Austin

yes VSYNC input Is an edge triggered, as describes

i.MX6DQ Datasheet (rev.4, 7/2015)

http://cache.freescale.com/files/32bit/doc/data_sheet/IMX6DQCEC.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Austin

yes VSYNC input Is an edge triggered, as describes

i.MX6DQ Datasheet (rev.4, 7/2015)

http://cache.freescale.com/files/32bit/doc/data_sheet/IMX6DQCEC.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thank you for the clarification. I had read this portion in the reference manual but was confused by the text which says '(all the timings correspond to straight polarity of the corresponding signals)' which I took to mean that the signal was level triggered, not edge triggered. Do you have any insight into what is meant by this phrase in the reference manual?

Regards

Austin