- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: IMX8MN RMII interface bringup

IMX8MN RMII interface bringup

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In our custom board based on IMX8MN, we are facing issue in RMII Ethernet interface.

Below is the device tree configuration.

pinctrl_fec1: fec1grp {

fsl,pins = <

MX8MN_IOMUXC_ENET_MDC_ENET1_MDC 0x3

MX8MN_IOMUXC_ENET_MDIO_ENET1_MDIO 0x23

MX8MN_IOMUXC_ENET_TXC_ENET1_RGMII_TXC 0x4000001f

MX8MN_IOMUXC_ENET_TD1_ENET1_RGMII_TD1 0x56

MX8MN_IOMUXC_ENET_TD0_ENET1_RGMII_TD0 0x56

MX8MN_IOMUXC_ENET_RD1_ENET1_RGMII_RD1 0x56

MX8MN_IOMUXC_ENET_RD0_ENET1_RGMII_RD0 0x56

MX8MN_IOMUXC_ENET_RXC_ENET1_RX_ER 0x56

MX8MN_IOMUXC_ENET_RX_CTL_ENET1_RGMII_RX_CTL 0x56

MX8MN_IOMUXC_ENET_TX_CTL_ENET1_RGMII_TX_CTL 0x56

MX8MN_IOMUXC_ENET_RD2_GPIO1_IO28 0x19 /* Interrupt */

MX8MN_IOMUXC_GPIO1_IO00_GPIO1_IO0 0x116 /* Reset */

>;

};

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_fec1>;

phy-mode = "rmii";

phy-handle = <ðphy0>;

phy-reset-gpios = <&gpio1 0 GPIO_ACTIVE_LOW>;

fsl,magic-packet;

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@0 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <0>;

interrupt-parent = <&gpio1>;

interrupts = <28 IRQ_TYPE_EDGE_FALLING>;

};

};

};

After booting, we are able to see Ethernet driver log

[ 6.069688] Micrel KSZ8081 or KSZ8091 30be0000.ethernet-1:00: attached PHY driver [Micrel KSZ8081 or KSZ8091] (mii_bus:phy_addr=30be0000.ethernet-1:00, irq=77)

But when we connect Ethernet cable to the board, the link is not getting detected. I found one reference dts imx8mq-ddr3l-val.dts, where a RMII interface has been configured.

pinctrl_fec1: fec1grp {

fsl,pins = <

MX8MQ_IOMUXC_ENET_MDC_ENET1_MDC 0x3

MX8MQ_IOMUXC_ENET_MDIO_ENET1_MDIO 0x23

MX8MQ_IOMUXC_ENET_TD2_ENET1_TX_CLK 0x4000001f

MX8MQ_IOMUXC_ENET_TD1_ENET1_RGMII_TD1 0x56

MX8MQ_IOMUXC_ENET_TD0_ENET1_RGMII_TD0 0x56

MX8MQ_IOMUXC_ENET_RD1_ENET1_RGMII_RD1 0x56

MX8MQ_IOMUXC_ENET_RD0_ENET1_RGMII_RD0 0x56

MX8MQ_IOMUXC_ENET_RXC_ENET1_RX_ER 0x56

MX8MQ_IOMUXC_ENET_RX_CTL_ENET1_RGMII_RX_CTL 0x56

MX8MQ_IOMUXC_ENET_TX_CTL_ENET1_RGMII_TX_CTL 0x56

>;

};

In the above pin mux configuration it uses MX8MQ_IOMUXC_ENET_TD2_ENET1_TX_CLK, but we are using MX8MN_IOMUXC_ENET_TXC_ENET1_RGMII_TXC.

Whether ENET1_TX_CLK and ENET1_RGMII_TXC are same..? Will it cause a problem in link detection.

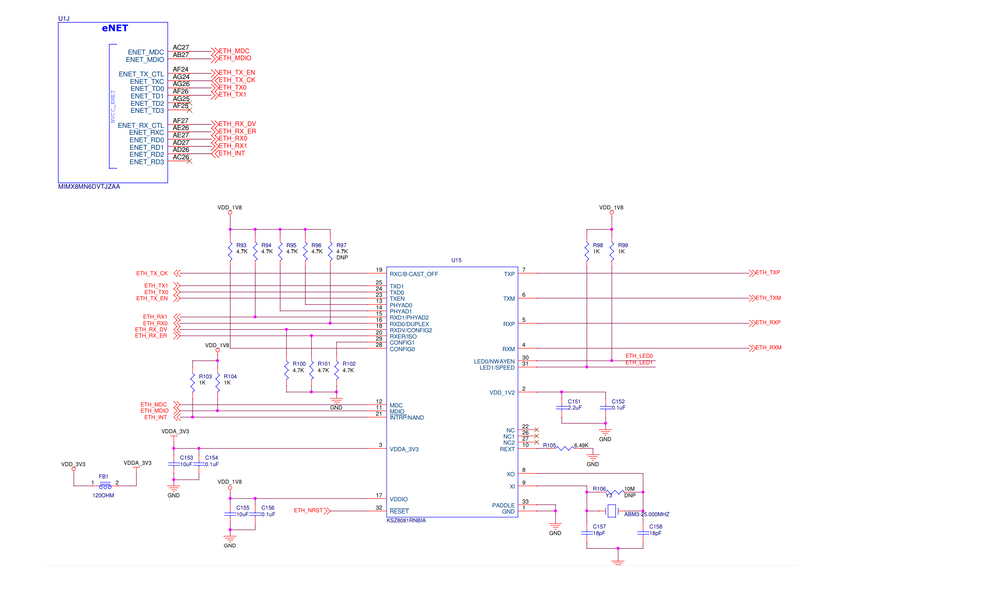

Below is our custom board RMII ethernet connection schematic.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi love1ymano

rmii clocks are described in Table 11-78. ENET External Signals

i.MX 8M Nano Applications Processor Reference Manual

ENET1_TX_CLK - Used as RMII clock - pad ENET_TD2 (ALT1)

sect.8.2.5.22 Pad Mux Register (IOMUXC_SW_MUX_CTL_PAD_ENET_TD2)

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Problem was resolved at your end ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi love1ymano

rmii clocks are described in Table 11-78. ENET External Signals

i.MX 8M Nano Applications Processor Reference Manual

ENET1_TX_CLK - Used as RMII clock - pad ENET_TD2 (ALT1)

sect.8.2.5.22 Pad Mux Register (IOMUXC_SW_MUX_CTL_PAD_ENET_TD2)

Best regards

igor