- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hello Everyone,

We are developing a custom board based on IMX7 sabreSD. We are planning to support eMMC boot and SD boot. So I studied about fuse options in IMX7. Below is the summery of understanding.

Various boot mode and boot selection of device is based on BOOT_MODE and BOOT_CFG values as per TRM. Here BOOT_MODE[1:0] is based on hardware settings and BOOT_CFG values are to be fused into OTP registers for the first time. The 6.3.3 Fusemap Descriptions Table of TRM gives the fuse address values of BOOT_CFG value is 0x470. It also gives the fuse names and fuse functions of 0x470[19:0], 0x470[25], 0x470[27], 0x470[28],0x470[29] bits.

Now below are my queries related to this fuse map.

- 0x470 offset is mapped to OCOTP_BOOT_CFG0 OTP register. So I need to write one time value to this fuse map based on my boot device selection. Now I am figuring out the 32 bit value for this fuse map. From the TRM, I have managed to find the values of 0x470[15:0] and 0x470[28] which is BT_FUSE_SEL. Now my question is, how can I select the other values for this 32 bit fuse OTP register? I mean, I want to know the valid values for 0x470[31:16] excluding 0x470[28] ? Where can I find those details?

- Also can any one confirm, that above understanding about fuse map in IMX7 is correct? Specifically Is the fuse map OTP register OCOTP_BOOT_CFG0 correct?

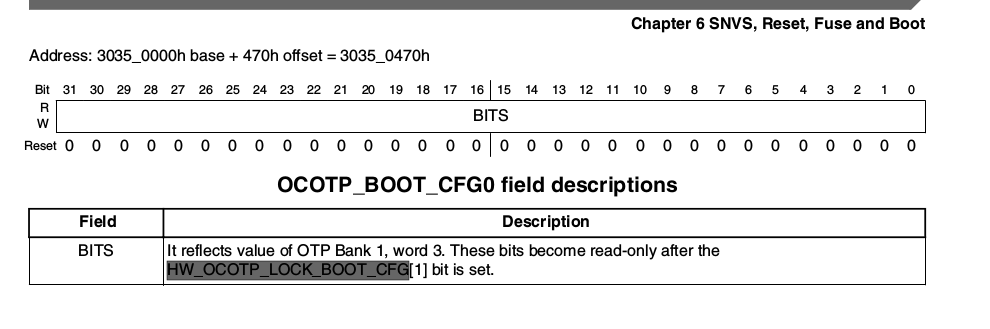

- In the OTP register section of OCOTP_BOOT_CFG0, I can see below description

Can you please explain, what's that "HW_OCOTP_LOCK_BOOT_CFG[1]" bit is? Which register I need to set that bit?

Thank You in advance.

Regards,

Gopinath S

已解决! 转到解答。

Hello,

You are right, section 6.3.3 Fusemap Descriptions Table of i.MX 7Dual Applications Processor Reference Manual,

Rev. 0.1, 08/2016 provides common for all boot configurations (including BOOT_CFG : 0x470[19:0]) options.

BOOT_CFG : 0x470[19:0] contains also specific for boot device settings, that are described in section 6.6 System Boot.

The bits, that are not described - are not used, and should not be touched.

The LOCK bit is located at 0x400[3:2] - BOOT_CFG_LOCK ( section 6.3.3).

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hello,

You are right, section 6.3.3 Fusemap Descriptions Table of i.MX 7Dual Applications Processor Reference Manual,

Rev. 0.1, 08/2016 provides common for all boot configurations (including BOOT_CFG : 0x470[19:0]) options.

BOOT_CFG : 0x470[19:0] contains also specific for boot device settings, that are described in section 6.6 System Boot.

The bits, that are not described - are not used, and should not be touched.

The LOCK bit is located at 0x400[3:2] - BOOT_CFG_LOCK ( section 6.3.3).

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Yuri,

Thank You for your prompt response.When you say "should not be touched" means I cannot set that bit to high (1). Am I correct? Because I am planning to use MFG tool's ucl2.xml file to fuse the SOM.

For Eg in case of IMX6 it is like,

<CMD state="Updater" type="push" body="$ echo 0x4060 > /sys/fsl_otp/HW_OCOTP_CFG4">fuse prog 0 5 0x4060</CMD> <CMD state="Updater" type="push" body="$ echo 0x00000010 > /sys/fsl_otp/HW_OCOTP_CFG5">fuse prog 0 6 0x00000010</CMD> |

So I guess writing '0' to other bits will not cause any issues. Right?