- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: I.MX6SX SoloX Debugging

I.MX6SX SoloX Debugging

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I.MX6SX SoloX Debugging

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello All,

Does Freescale have any guidelines for debugging both cores of the I.MX6SX (I.MX6 SoloX) processor?

We are hoping to do real-time debugging of the A9 and M4 cores under a Linux host with a gnu compiler.

It looks like the ARM DS-5 studio and DSTREAM debugger may be listed on Freescale's website. However, these options are out of our price range. Are there any alternatives?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello all,

I finally found the correct set up:

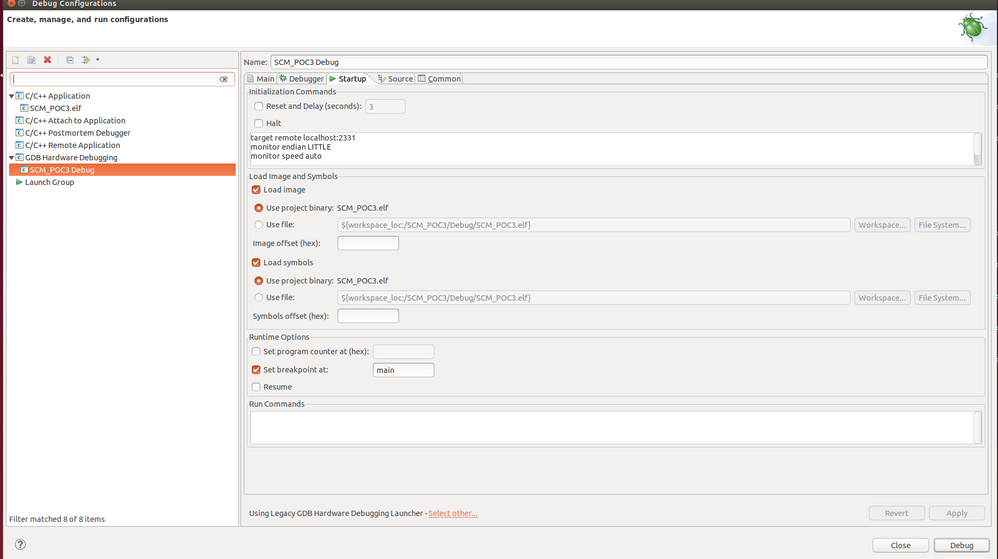

Then I try to connect to JLinkGDBServer from Eclipse with the following debugger settings:

Run->Debug configurations:

Debugger tap

GDB setup

GDB command: gcc-arm-none-eabi-4_9-2015q1/bin/arm-none-eabi-gdb

Command set: srtandard

Protocol version: mi

Verbose console mode: not checked

Remote Target:

Use remote target: checked

JTAG device: Generic TCP/IP

host name or IP address: localhost

port number: 2331

Start up tap:

Reset and deley seconds: not checked

Halt: not checked

Commands:

target remote localhost:2331

monitor endian LITTLE

monitor speed auto

Load Image and Symbols:

Load image: checked

Use project binary: SCM_POC3.elf

Image offset (hex):

Load symbols: checked

Use project binary: SCM_POC3.elf

Image offset (hex):

Runtime Options:

Set program counter at (hex):

Set breakpoint at: main

Resume: not checked

Run commands: none

Everything else was correct. It seems debug reset is not supported on the cortex-m as it is stated in the RM:

7.4.1 Clock/Reset/Power

CDBGPWRUPREQ and CDBGPWRUPACK are the handshake signals between the

DAP and the clock control module to ensure debug power and clocks are turned on. If the

debug components are always powered on, the handshake becomes a mechanism to turn

debug clocks on. Similarly, there is a register bit in the CCM which allows internal

software to turn debug clocks on as well because the CDBGPWRUPREQ is in the TCLK

domain and is inaccessible to software.

The Cortex-A9 and VSP cores can receive resets from the following sources:

• Debug Reset (CDBGRSTREQ bit within the SWJ-DP CTRL/STAT register of the

DAP) in the TCLK domain. This allows the debug tools to reset the debug logic.

• System POR reset

Conversely, the debug system is capable of generating a system reset via a request bit in

the MDM-AP control register. This allows the debugger to hold the system in reset.

It doesn't say anything about cortex-m4 debug reset.

Best regards,

Oscar.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey oscargarciaabad,

Do you have OS awareness with this setup for M4? Can i ask which IDE are you using for the A9 part?

Thanks,

Evgeny

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Oscar,

I have tried your directions. I load the M4 binary and I can see it running in my console window. As soon I begin to debug with Eclipse, the J-Link resets the entire board, and the A9 resets, as well. This causes the GDB to crash. I looked through the Startup tab in Eclipse for the debug configuration but I cannot find the 'Reset and Delay' box to un-check. Any advice to get the J-Link NOT to reset the target? I've also tried 'Connect to a Running Target'.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sam,

Next you can see my configuration. This is for Eclipse Mars.2. I didn't try this with older eclipse versions. You can se the "Reset and delay" checkbox at the top of the image.

I hope this solve your problem.

Best regards,

Oscar.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Oscar,

Now I see. For the debug configuration, I was using the 'GDB SEGGERJ-Link Debugger' option, which doesn't have a reset and delay option. I will use the 'GDB Hardware Debugging' option. I am using Windows, and I am assuming that I will first manually start the Segger J-Link GDB executable, and see which port it is using, and I can enter that info into Eclipse.

Any ideas if this J-Link script will work on an IMX7?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey Sam,

Were you able to get this thing working on windows using eclipse?

Thanks,

Evgeny

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello All,

I built the FReeRTOS hello_world demo application for the Cortex-M4 of the i.MX6SX (BSP downloaded from here: i.MX 6 Series Software and Development Tool|NXP ). I'm building the application under ubuntu 14.04 with Eclipse MARS.2 and the toolchain gcc-arm-none-eabi-4_9-2015q1-20150306-linux. I can build an OCRAM debug binary and run it succesfully, on a sabre SD soloX board, with the following commands under u-boot (after burning the binary into the first partition (boot) of an SDCARD built under yocto Fido):

fatload mmc 2:1 0x00910000 SCM_PO.bin

dcache flush

bootaux 0x00910000

After this I can connect to the cortex-M4 CPU using JLinkGDBServer program with the script provided by Nathan:

JLinkGDBServer -device cortex-m4 -scriptfile Default.JLinkScript.M4

Then I try to connect to JLinkGDBServer from Eclipse with the following debugger settings:

Run->Debug configurations:

Debugger tap

GDB setup

GDB command: gcc-arm-none-eabi-4_9-2015q1/bin/arm-none-eabi-gdb

Command set: srtandard

Protocol version: mi

Verbose console mode: not checked

Remote Target:

Use remote target: checked

JTAG device: Generic TCP/IP

host name or IP address: localhost

port number: 2331

Start up tap:

Reset and deley seconds: checked. 3

Halt: checked

Commands:

target remote localhost:2331

monitor endian LITTLE

monitor speed 1000

monitor reset 0

monitor sleep 100

monitor speed auto

Load Image and Symbols:

Load image: checked

Use project binary: SCM_POC3.elf

Image offset (hex):

Load symbols: checked

Use project binary: SCM_POC3.elf

Image offset (hex):

Runtime Options:

Set program counter at (hex):

Set breakpoint at: main

Resume: not checked

Run commands: none

Then I debug the application. The code is downloaded to the target succesfully, but the debugger doesn't pauses at main instead it pauses on the file startup_MCIMX6X_M4.S line 207:

Reset_Handler:

cpsid i /* Mask interrupts */ --> it pauses in this line

#ifndef __NO_SYSTEM_INIT

bl SystemInit

#endif

When I click on the continue button the applications terminates due a SIGTRAP.

Here is the Eclipse console output:

Reading symbols from /home/oscar/Projects/IMX6_SoloX/Cortex-M4/workspace/SCM_POC3/Debug/SCM_POC3.elf...symbol-file /home/oscar/Projects/IMX6_SoloX/Cortex-M4/workspace/SCM_POC3/Debug/SCM_POC3.elf

done.

0x0091061c in UART_ReceiveDataPolling (base=0x421e8000, rxBuff=0x200002d7 <ucHeap+563> "", rxSize=0) at /home/oscar/Projects/IMX6_SoloX/Cortex-M4/FreeRTOS/FreeRTOS_BSP_1.0.0_iMX6SX/platform/utilities/src/debug_console_imx.c:375

375 while (!UART_GetStatusFlag((UART_Type*)base, uartStatusRxDataReady));

monitor endian LITTLE

monitor reset 0

monitor sleep 100

monitor speed auto

tbreak main

Temporary breakpoint 1 at 0x9133da: file ../src/Application/main.c, line 71.

Program received signal SIGTRAP, Trace/breakpoint trap.

0x00000000 in ?? ()

And the JLinkGDBServer output:

JLinkARM.dll V5.10q (DLL compiled Mar 4 2016 16:05:00)

-----GDB Server start settings-----

GDBInit file: none

GDB Server Listening port: 2331

SWO raw output listening port: 2332

Terminal I/O port: 2333

Accept remote connection: yes

Generate logfile: off

Verify download: off

Init regs on start: off

Silent mode: off

Single run mode: off

Target connection timeout: 0 ms

------J-Link related settings------

J-Link Host interface: USB

J-Link script: /home/oscar/Projects/IMX6_SoloX/Debugger/scripts/Default.JLinkScript.M4

J-Link settings file: none

------Target related settings------

Target device: cortex-m4

Target interface: JTAG

Target interface speed: 1000kHz

Target endian: little

Connecting to J-Link...

J-Link is connected.

Firmware: J-Link V10 compiled Mar 2 2016 14:01:26

Hardware: V10.10

S/N: 600100354

Feature(s): RDI, FlashBP, FlashDL, JFlash, GDB

Checking target voltage...

Target voltage: 3.29 V

Listening on TCP/IP port 2331

Connecting to target...WARNING: At least one of the connected devices is not JTAG compliant (IEEE Std 1149.1, 7.1.1.d, IR-cells). (NumDevices = 4, NumBitsSet = 3)

J-Link found 4 JTAG devices, Total IRLen = 17

JTAG ID: 0x4BA00477 (Cortex-M4)

Connected to target

Waiting for GDB connection...Connected to 127.0.0.1

Reading all registers

Read 4 bytes @ address 0x0091061C (Data = 0xF44F68F8)

Read 4 bytes @ address 0x200002CC (Data = 0x009105B5)

Read 4 bytes @ address 0x200002CC (Data = 0x009105B5)

Read 4 bytes @ address 0x009105B4 (Data = 0x461879FB)

Read 4 bytes @ address 0x200002C8 (Data = 0x200002D0)

Read 4 bytes @ address 0x200002C4 (Data = 0x421E8000)

Read 4 bytes @ address 0x200002C0 (Data = 0x200002D7)

Reading 8 bytes @ address 0x200002D7

Read 4 bytes @ address 0x200002BC (Data = 0x00000000)

Read 4 bytes @ address 0x200002C4 (Data = 0x421E8000)

Read 4 bytes @ address 0x200002C0 (Data = 0x200002D7)

Reading 8 bytes @ address 0x200002D7

Read 4 bytes @ address 0x200002BC (Data = 0x00000000)

GDB closed TCP/IP connection

Connected to 127.0.0.1

Reading all registers

Read 4 bytes @ address 0x0091061C (Data = 0xF44F68F8)

Read 4 bytes @ address 0x200002CC (Data = 0x009105B5)

Read 4 bytes @ address 0x200002CC (Data = 0x009105B5)

Read 4 bytes @ address 0x009105B4 (Data = 0x461879FB)

Read 4 bytes @ address 0x200002C8 (Data = 0x200002D0)

Read 4 bytes @ address 0x200002C4 (Data = 0x421E8000)

Read 4 bytes @ address 0x200002C0 (Data = 0x200002D7)

Reading 8 bytes @ address 0x200002D7

Read 4 bytes @ address 0x200002BC (Data = 0x00000000)

Read 4 bytes @ address 0x200002C4 (Data = 0x421E8000)

Read 4 bytes @ address 0x200002C0 (Data = 0x200002D7)

Reading 8 bytes @ address 0x200002D7

Read 4 bytes @ address 0x200002BC (Data = 0x00000000)

Target endianess set to "little endian"

Target interface speed set to 1000 kHz

Read 4 bytes @ address 0x200002C4 (Data = 0x421E8000)

Read 4 bytes @ address 0x200002C0 (Data = 0x200002D7)

Reading 8 bytes @ address 0x200002D7

Read 4 bytes @ address 0x200002BC (Data = 0x00000000)

WARNING: Could not set S_RESET_ST

WARNING: CPU did not halt after reset.

WARNING: CPU could not be halted

WARNING: CPU did not halt after reset.

WARNING: CPU could not be halted

WARNING: CPU did not halt after reset.

WARNING: CPU could not be halted

WARNING: S_RESET_ST not cleared

Resets core & peripherals via SYSRESETREQ & VECTRESET bit.

WARNING: Failed to read memory @ address 0x200002DC

WARNING: Failed to read memory @ address 0x200002DC

Sleep 100ms

Select auto target interface speed (4000 kHz)

Downloading 576 bytes @ address 0x00910000

Downloading 4096 bytes @ address 0x00910240

Downloading 4096 bytes @ address 0x00911240

Downloading 4096 bytes @ address 0x00912240

Downloading 4096 bytes @ address 0x00913240

Downloading 1240 bytes @ address 0x00914240

Downloading 8 bytes @ address 0x00914718

Downloading 4 bytes @ address 0x00914720

Downloading 4 bytes @ address 0x00914724

Downloading 120 bytes @ address 0x00914728

Writing register (PC = 0x00910310)

Read 4 bytes @ address 0x00910310 (Data = 0x00000000)

Read 2 bytes @ address 0x009133DA (Data = 0x0000)

Read 2 bytes @ address 0x009133DA (Data = 0x0000)

Read 2 bytes @ address 0x009133DA (Data = 0x0000)

Setting breakpoint @ address 0x009133DA, Size = 2, BPHandle = 0x0001

Starting target CPU...

ERROR: CPU is not halted

ERROR: Can not read register 15 (R15) while CPU is running

Reading all registers

ERROR: Can not read register 0 (R0) while CPU is running

ERROR: Can not read register 1 (R1) while CPU is running

ERROR: Can not read register 2 (R2) while CPU is running

ERROR: Can not read register 3 (R3) while CPU is running

ERROR: Can not read register 4 (R4) while CPU is running

ERROR: Can not read register 5 (R5) while CPU is running

ERROR: Can not read register 6 (R6) while CPU is running

ERROR: Can not read register 7 (R7) while CPU is running

ERROR: Can not read register 8 (R8) while CPU is running

ERROR: Can not read register 9 (R9) while CPU is running

ERROR: Can not read register 10 (R10) while CPU is running

ERROR: Can not read register 11 (R11) while CPU is running

ERROR: Can not read register 12 (R12) while CPU is running

ERROR: Can not read register 13 (R13) while CPU is running

ERROR: Can not read register 14 (R14) while CPU is running

ERROR: Can not read register 15 (R15) while CPU is running

ERROR: Can not read register 16 (XPSR) while CPU is running

ERROR: Can not read register 17 (MSP) while CPU is running

ERROR: Can not read register 18 (PSP) while CPU is running

ERROR: Can not read register 24 (PRIMASK) while CPU is running

ERROR: Can not read register 25 (BASEPRI) while CPU is running

ERROR: Can not read register 26 (FAULTMASK) while CPU is running

ERROR: Can not read register 27 (CONTROL) while CPU is running

ERROR: Can not read register 32 (FPSCR) while CPU is running

ERROR: Can not read register 33 (FPS0) while CPU is running

ERROR: Can not read register 34 (FPS1) while CPU is running

ERROR: Can not read register 35 (FPS2) while CPU is running

ERROR: Can not read register 36 (FPS3) while CPU is running

ERROR: Can not read register 37 (FPS4) while CPU is running

ERROR: Can not read register 38 (FPS5) while CPU is running

ERROR: Can not read register 39 (FPS6) while CPU is running

ERROR: Can not read register 40 (FPS7) while CPU is running

ERROR: Can not read register 41 (FPS8) while CPU is running

ERROR: Can not read register 42 (FPS9) while CPU is running

ERROR: Can not read register 43 (FPS10) while CPU is running

ERROR: Can not read register 44 (FPS11) while CPU is running

ERROR: Can not read register 45 (FPS12) while CPU is running

ERROR: Can not read register 46 (FPS13) while CPU is running

ERROR: Can not read register 47 (FPS14) while CPU is running

ERROR: Can not read register 48 (FPS15) while CPU is running

ERROR: Can not read register 49 (FPS16) while CPU is running

ERROR: Can not read register 50 (FPS17) while CPU is running

ERROR: Can not read register 51 (FPS18) while CPU is running

ERROR: Can not read register 52 (FPS19) while CPU is running

ERROR: Can not read register 53 (FPS20) while CPU is running

ERROR: Can not read register 54 (FPS21) while CPU is running

ERROR: Can not read register 55 (FPS22) while CPU is running

ERROR: Can not read register 56 (FPS23) while CPU is running

ERROR: Can not read register 57 (FPS24) while CPU is running

ERROR: Can not read register 58 (FPS25) while CPU is running

ERROR: Can not read register 59 (FPS26) while CPU is running

ERROR: Can not read register 60 (FPS27) while CPU is running

ERROR: Can not read register 61 (FPS28) while CPU is running

ERROR: Can not read register 62 (FPS29) while CPU is running

ERROR: Can not read register 63 (FPS30) while CPU is running

ERROR: Can not read register 64 (FPS31) while CPU is running

WARNING: Failed to read memory @ address 0x00000000

Removing breakpoint @ address 0x009133DA, Size = 2

WARNING: Failed to read memory @ address 0x00000000

What Am I doing wrong?

Thanks in advance.

Oscar.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nathan,

If you use the Jlink.

You can follow the Jlink document to write down script to debug A9 or M4.

But so far, it only can debug one core at one time.

Attached files are for A9 and M4.

A9 debug: Please rename the Default.JLinkScript.A9 to Default.JLinkScript and overwrite Default.JLinkScript in the Jlink folder.

M4 debug: Please rename the Default.JLinkScript.M4 to Default.JLinkScript and overwrite Default.JLinkScript in the Jlink folder.

If any problem, please contact jink to get further support.

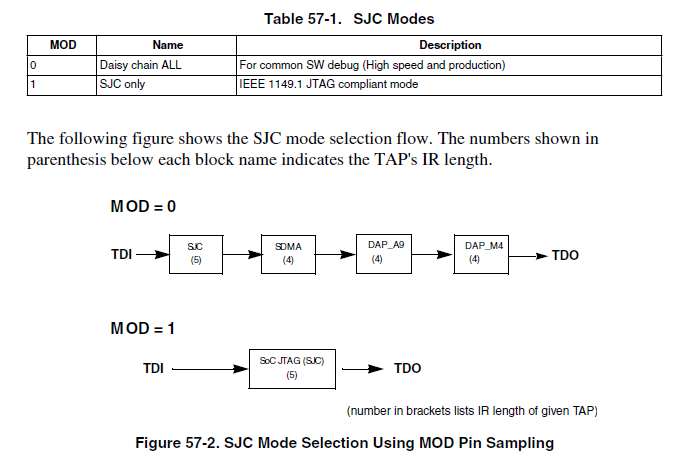

TAP's IR length is in the reference manual

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nathan

in general one can use any debugger which supports Cortex-A9 and M4,

for that one can look at debugger datasheet or contact its vendor.

Seems one can use J-Link, Lauterbach, also SDK have some scripts for debugger

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What's the general Idea of Freescale to debug applications within the Cortex-M4 core of the i.MX6 SoloX?

Are there any IAR setup macros (*.mac) files available to debug the application on the SABRE SoloX?

SABRE SoloX evaluation board (MCIMX6SX-SDB):

SABRE Board Reference Design|Freescale

According to the MQX i.MX6 SoloX release notes chapter 2.2.2:

Although IAR and DS5 are supported to build the MQX RTOS and examples, the debugger part of these IDE tools are not enabled.

Only TRACE32 is able to debug the programs built from ARM-GCC, IAR and DS5

You are kidding me if it is intended to do printf debugging to develop applications on the Cortex-M4 core? :smileyconfused:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If you are speaking about IAR, there are lot of Cortex-M4

examples with debugger in its IAR IDE WorkBench.

I think you can use just generic Cortex-M4 examples.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The problem is not building and linking an application with IAR for the Cortex-M4, it's the debugging!

As written in the application note, Freescale did not ship setup macros and flash downloaders for the SABRE SoloX evalboard.

Without setup macros for the SoloX the Cortex-M4 cannot be started, because it has to be enabled by the Cortex-A...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

what "setup macros" are you speaking about ?

Could you give some example of such "setup macros" ?

Does "setup macros" depend on IDE: for example DS5, IAR ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

A setup macro performs operations before the actual debugging session can start.

In the given example of the SoloX, we first have to start the Cortex-A8 in order to release the Cortex-M3. To load the code from the debugger into the external DDR RAM, the external DDR RAM should be initialized properly in order to get the full speed.

Or as usual, because Freescale does not provide those configuration files, the examples only work with the internal RAM.

Have a look at the Freescale MQX i.MX6 SoloX Release Notes (MQXIMX6SXRN) which you have posted in the forum:

Re: i.MX6SoloX running MQX in the Cortex-A9 core?

Every IDE has those setup scripts / macros:

- in TRACE32 those files are "script files" (*.cmm)

- in IAR those are "setup macros" (*.mac)

- in ARM-DS5 they are called init scripts (*.ds)

In the application note chapter 3.2.2 it is described for TRACE32 which steps have to be performed (attach_imx6sx_m4.cmm).

Now the question again:

Will freescale provide us Debugger support for IAR on the Cortex-M4 core of the i.MX6 SoloX?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

AFAIR before such debugger support was provided by IAR

since SoloX is quite new, seems it will be supported some time later.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor. 7 months have passed and I still cannot find the IAR setup macro for M4 debugging, nor any official A9 project for IAR. Do you know about something available? Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Petr

IAR listed i.MX6SX as supported device with "HW Debug" support

seems you can contact them for more details

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for quick reply. I am aware of the device support in IAR, but the support here means only an item in the device list, but no setup macro and no example project. Also the j-Link driver does not support that device.

- Regarding the examples, IAR refers to Freescale.

- Regarding the j-Link driver, IAR refers to Segger.

- Following your post, Freescale refers to IAR.

- Segger says the driver is supported by external scripts, available at I.MX6 SoloX Support - SEGGER - Support Wiki . At the same time they say M4 cannot be debugged without an A9 software enabling the M4 core. As expected, the MQX M4 demo project (hello) does not work with the script. They do not suggest where to get the A9 example.

- BiyongSUN below provided other j-Link scripts. I appreciate his effort, but I'm not able to run the MQX M4 hello project with his scripts, neither. For further support, he refers to Segger.

- I did not manage to find any simple A9 example. The handle points to Freescale. Who does Freescale refer to, so that the magic circle locks up?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

M4 needs A9 to boot up.

Once M4 gets boot up.

You can use the jlink attach the M4 with the script.

The script is verified on the SoloX SDB board. Used in some customer project.

Maybe your jlink firmware and software versions are different.

My experience is without the script. The jlink, which can debug i.MX6DQ/DLS before, will attach the M4 because of the ir length.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Petr

below simple A9 example

in general I would suggest to contact local fae for questions

regarding more support. Also for customer customizations

FSL has Freescale Professional Services:

http://www.freescale.com/webapp/sps/site/overview.jsp?code=CW_PROFESSIONAL

Best regards

igor