- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

How to set the 1.2/1.5 Gbps speed in the example source code?

As the datasheet, MIPI Display Serial Interface(MIPI DSI)

- 2 data lanes interface with up to 1.5 GHz bit rate clock.

I want to check it in the below example code(EVK example code).

How to set it?

NXP (1170/MCUEXPresso)Example code: (the attached file-MIMXRT1170-EVK\boards\evkmimxrt1170\driver_examples\csi\mipi_rgb\cm7/board.c )

Below source code show as 60MHz, but I want to change CLK for 1.2/1.5Gbps

<Below >====================================================

- CSI2 CLK 설정.

/* This clock should be equal or faster than the receive byte clock,

* D0_HS_BYTE_CLKD, from the RX DPHY. For this board, there are two

* data lanes, the MIPI CSI pixel format is 16-bit per pixel, the

* max resolution supported is 720*1280@30Hz, so the MIPI CSI2 clock

* should be faster than 720*1280*30 = 27.6MHz, choose 60MHz here.

*/

→ details show 60Mhz -> MIPI speed : 60Mhz ?

const clock_root_config_t csi2ClockConfig = {

.clockOff = false,

.mux = 5,

.div = 8,

};

→ .mux = 5 value, kCLOCK_CSI2_ClockRoot_MuxSysPll3Out(480Mhz) , div = 8... Is it right??.

Up means '480Mhz/div8 = 60Mhz' .. Is it right?

If it is right . How to set as " 1.2/1.5 Gbps clock speed"?

/* CSI2 */

kCLOCK_CSI2_ClockRoot_MuxOscRc48MDiv2 = 0U, /*!< CSI2 mux from MuxOscRc48MDiv2. */

kCLOCK_CSI2_ClockRoot_MuxOsc24MOut = 1U, /*!< CSI2 mux from MuxOsc24MOut. */

kCLOCK_CSI2_ClockRoot_MuxOscRc400M = 2U, /*!< CSI2 mux from MuxOscRc400M. */

kCLOCK_CSI2_ClockRoot_MuxOscRc16M = 3U, /*!< CSI2 mux from MuxOscRc16M. */

kCLOCK_CSI2_ClockRoot_MuxSysPll2Pfd2 = 4U, /*!< CSI2 mux from MuxSysPll2Pfd2. */

kCLOCK_CSI2_ClockRoot_MuxSysPll3Out = 5U, /*!< CSI2 mux from MuxSysPll3Out. */

kCLOCK_CSI2_ClockRoot_MuxSysPll2Pfd0 = 6U, /*!< CSI2 mux from MuxSysPll2Pfd0. */

kCLOCK_CSI2_ClockRoot_MuxVideoPllOut = 7U, /*!< CSI2 mux from MuxVideoPllOut. */

已解决! 转到解答。

Hi,

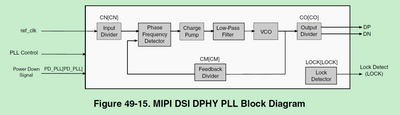

MIPI DSI has its own DPHY PLL to generate DPI pixel clock.

More detailed info, please refer RT1170 reference manual chapter 49.3.5.2 DPHY PLL & chapter 49.3.5.3 DPHY Programming

Wish it helps.

Mike

Hi,

MIPI DSI has its own DPHY PLL to generate DPI pixel clock.

More detailed info, please refer RT1170 reference manual chapter 49.3.5.2 DPHY PLL & chapter 49.3.5.3 DPHY Programming

Wish it helps.

Mike