- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

How to enable uBoot booting from Parallel Nor Flashes in Parallel Flash Mode Flex-SPI on IMX8QM

Hi,

We are using two serial nor flashes connected to portA0 and PortB0 of flexspi0, We have configured our boot mode pin settings for the FlexSpi Boot as default. In this mode, we are observing uboot binary is being loaded on only one individual flash and booting up from the same. but now we want to load uboot binary in both flashes by enabling parallel flash mode and booting up the device in parallel flash mode by default. can you please provide some mechanism on how to enable booting from parallel nor flashes that are connected to FlexSpi as we are accessing both the flashes in Parallel flash configuration in our BM and Application as well.

Hi @GopiKrishna ,

I hope you're doing great! For details on parallel mode for FlexSPI you can review the i.MX 8QM Reference Manual Section 19.3 Flexible SPI Controller (https://www.nxp.com/webapp/Download?colCode=IMX8QMRM). Let me know if this was of any help.

Best regards.

Hector.

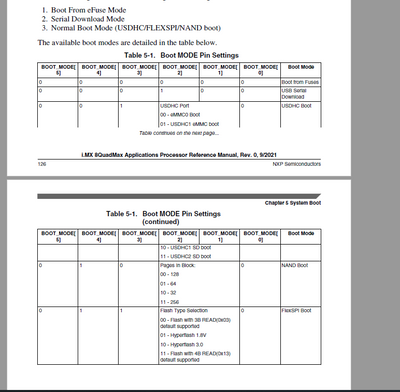

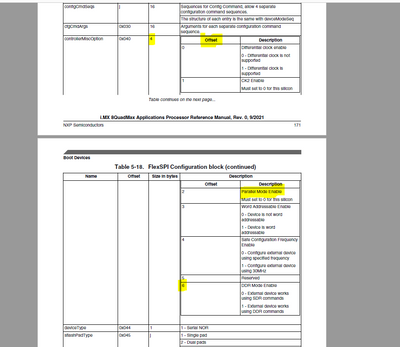

Greetings! Actually, My query was not about how to implement Parallel Flash mode in Flex-Spi. We have already successfully developed our driver to run in Parallel Flash Mode and are able to access both Flash chips in parallel mode. My question was about how we can select the default boot device configuration as Flex-Spi with Parallel flash mode enabled. We have referred to the section 5.3.1 Boot Mode Pin Settings and 5.8.3 FlexSPI serial flash memory boot and configured our Boot mode settings. with our current configuration, we are able to set the Flex-Spi flash device as the default boot device whereas it was booting only from one Individual flash. but our requirement is it should boot in Parallel Flash Mode from both flash devices connected to Flex-Spi ports A0 and B0. Our current boot device configuration is as per Table 5-8. Boot Device Selection is 011000. so can you please help us if we have to do any further settings to configure the default boot device selection as FlexSpi Boot with Parallel Flash Mode enabled?

2) We have gone through the 5.8.3.3 FlexSPI configuration parameters but here we are seeing one setting is there to enable the parallel flash mode but it was not so detailed and one more observation is for a given size of 4 bytes there are 6 offsets given can you please elaborate more on this and how to enable this parallel flash setting?

I didn't try it on iMX8, from experience with parallel flash with older QuadSPI module:

Were you able to adjust in FlexSPI FCFB struct in QSPI flash at least serialClkFreq? So that FCFB is read at default low clock, then ROM switches to clearly higher clock specified in serialClkFreq and continues reading IVT and the rest of U-Boot at higher clock? At least you should start from verifying your changes in FCFB are applying.

When you are in touch with FCFB, try configuring FCFB for parallel mode. Don't forget about special parallel read command in LUT, which must provided via FCFB as well. When parallel FCFB is done, you need to program IVT and the rest of U-Boot image in parallel mode starting from right parallel mode flash offset. FCFB has to be programmed in single chip mode to just flash A (, or as well the copy of it in single chip mode to flash B, which won't be read by ROM anyway). Parallel mode, as you may know, interleaves data to A/B, FCFB should be readable from A in non parallel mode, so no data interleaving for FCFB.

For debugging JTAG access is very recommended to verify right IVT etc data is readable in QSPI address space in parallel mode. Though I don't how it will look in practice on iMX8. I hope FlexSPI isn't reset on faulty boot and it is possible to read QSPI AHB space with settings applied from FCFB. You may verify how it looks like in single FlexSPI mode.

Perhaps IVT is read along with FCFB in single mode, it is not very clear from iMX8RM. At least in the past only FCFB was read in single mode, the rest of image in parallel mode.

Edward

Hi @GopiKrishna ,

I hope you're doing great! I see, let me review this further and get back to you as soon as I have relevant information. Thank you.

Best regards,

Hector.

Greetings, I hope you had a good time reviewing my Query. I would like to appreciate your interest in this query. I was waiting for your response as I am in a hurry to Implement this requirement asap. so could you please update your comments earlier as possible?

Thanks

Gopikrishna

Hi @GopiKrishna ,

I hope you're doing great. On further analysis, we proceeded to escalate this issue with our internal team and we expect an answer as soon as possible. I'll personally let them know that this is an urgent issue. Thank you.

Best regards,

Hector.

Hi @GopiKrishna ,

I hope you're doing well. I'm prioritizing your case and I'm currently checking it with my team. Thank you for waiting. Expect an answer no later than tomorrow.

Best regards,

Hector.

Hi @hector_delgado,

Greetings! Hope you are doing great. I have been waiting for your response for the last few days. I was unable to reply back as the NXP community portal seems to be under maintenance and sign-in is not working. could you please provide your comments on this query as early as possible?

Hi @GopiKrishna ,

We are continuing communication with our ROM team and we're currently testing a tool that'll help us test and validate this configuration. I'll keep you updated with any further progress we make in the next few days. Thank you for your patience.

Best regards,

Héctor.

Hi @GopiKrishna ,

I hope you're doing great! Sorry for our slow responses, we're actively working on this issue and unfortunately it has been taking longer than we initially anticipated. I'll keep you updated with any news and progress we make. Thank you.

Best regards,

Hector.

Hi @GopiKrishna ,

Can you try the following?

- Use attached fspi_header to replace the standard one in mkimage under the scripts directory

- Build FSPI boot container using normal command

- Run ./splitter.sh flash.bin, using the FSPI container built in the previous step - this should create 2 images (ImageA and ImageB)

- Program flash devices in Linux

root@imx8dxlevk:~# cat /proc/mtd

dev: size erasesize name

mtd0: 80000000 00080000 "gpmi-nand"

mtd1: 04000000 00010000 "5d120000.spi-0"

mtd2: 04000000 00010000 "5d120000.spi-2"

root@imx8dxlevk:~# flash_erase /dev/mtd1 0 10

Erasing 64 Kibyte @ 90000 -- 100 % complete

root@imx8dxlevk:~# dd if=ImageA of=/dev/mtd1

1196+0 records in

1196+0 records out

612352 bytes (612 kB, 598 KiB) copied, 0.824804 s, 742 kB/s

root@imx8dxlevk:~# flash_erase /dev/mtd2 0 10

Erasing 64 Kibyte @ 90000 -- 100 % complete

root@imx8dxlevk:~# dd if=ImageB of=/dev/mtd2

1196+0 records in

1196+0 records out

612352 bytes (612 kB, 598 KiB) copied, 0.80508 s, 761 kB/s

root@imx8dxlevk:~#

After this parallel boot should be working. Let me know if this works for you.

Best regards,

Hector.

Hi @GopiKrishna ,

I hope you're doing great. Sorry for any inconvenience caused by some parts of our site being unavailable for the last few days. We're still reviewing your case with our internal escalations team. Thank you for waiting.

Best regards,

Hector.

Hi @GopiKrishna ,

I hope you're doing great. This is something that is supported, but the standard mkimage targets do not have an option by default to generate the appropriate binary that is interleaved between the 2 flash chips. I am discussing further with the ROM team to obtain a tool that can assist in generating the correct image, and then will test on one of the boards here internally and I'll get back to you with our results.

Thank you.

Best regards,

Hector.