- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Hi community,

I want to confirm about i.MX6SDL eCSPI behavior.

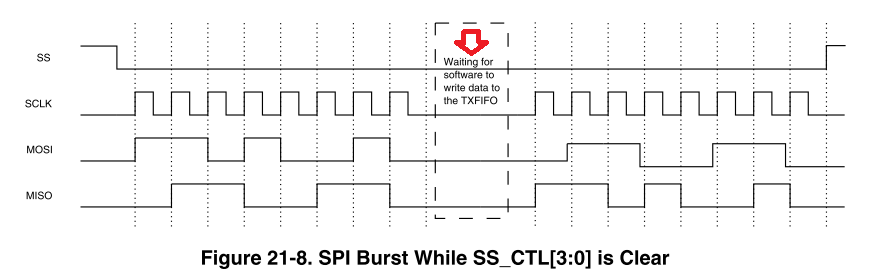

Please see the attached image, it shows Figure 21-8 in IMX6SDLRM (Rev.1).

I want to confirm about the "waiting" to start next burst transfer (the part of red arrow).

I believe, the term of "waiting" depends on SMC and XCH setting if eCSPI is master mode, right?

On the other hand, if eCSPI is slave mode, i.MX6SDL cannot control the timing when next burst starts.

So would you let me know how fast i.MX6SDL can load the TXDATA from FIFO to shift register (or load the RXDATA from shift register to FIFO) when SS_CTL=0?

And if there is a restriction about this burst transfer in slave mode, please tell me it.

(e.g. This transfer is only for master mode, SS should be negated after each burst in slave mode)

Best Regards,

Satoshi Shimoda

已解决! 转到解答。

The figure 21-8 relates to the master mode. The opposite device,

in slave mode, is waiting clocks and data from the master.

The load timing from / to the FIFO to / from shift register is unpredictable.

It would be better to say - the load timing from FIFO to shift register is

application dependent.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

The figure 21-8 relates to the master mode. The opposite device,

in slave mode, is waiting clocks and data from the master.

The load timing from / to the FIFO to / from shift register is unpredictable.

It would be better to say - the load timing from FIFO to shift register is

application dependent.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------