- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Getting Continuous PCM Clock from SSI INTERFACE?

Getting Continuous PCM Clock from SSI INTERFACE?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

We are using SLIC CODEC from Microsemi (LE9641). Le9641 Features a host port interface for communicating with VIOP processors and SOC using PCM and SPI. The host port interface supports PCM Clock rates of 1.024MHz, 1.536MHz, 2.048MHz. 3.073MHz, 4.096Mhz, 6.144MHz and 8.192Mhz with a Frame SYNC of 8KHz.

We have a custom designed board, where we have connected this PCM and SPI pins of CODEC IC with AUDMUX (AUD5) interface and the SPI interface of i.MX6D processor respectively.

We are able to communicate with the CODEC IC through SPI interface and are able to configure the SSI interface of the processor for PCM bus communication.

As per the requirement o the SLIC IC, PCM Clock should Come always and Frame Sync Signal should be of 8Khz. but we are getting PCM clock(2.048MHz) from the processor whenever we are playing an Raw data audio file using aplay command. Also the Frame sync signal is not coming of 8Khz(it is coming 32KHz). We tried to change the SSCI configuration registers value, but did not get any success yet.

Is there any way of getting the continuous PCM CLOCK from SSI interface if the Processor. We are configuring the SSI Interface in the Network Mode with Master I2S .

Please suggest any solution.

thanks

Sumit Sharma

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sumit

I am afraid that it is not possible to get continuous bit and frame sync clocks

using existing audio Linux drivers, as SSI is enabled only during playing audio.

Drivers description can be found in Chapter 29 i.MX_6_Linux_Reference_Manual.pdf

L3.14.28_1.0.0_iMX6QDLS_BUNDLE

Audio oversampling clock can be continuously outputted from CLKO pin,

as it is done on Sabre schematic spf-27392, AUD_MCLK, i.MX6_SABRE_SDP_DESIGNFILES .

and It can be configured in linux/../mach-imx/clk-imx6q.c

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

----------------------------------------------------------------------------------------------------------------------- !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sumit

I am afraid that it is not possible to get continuous bit and frame sync clocks

using existing audio Linux drivers, as SSI is enabled only during playing audio.

Drivers description can be found in Chapter 29 i.MX_6_Linux_Reference_Manual.pdf

L3.14.28_1.0.0_iMX6QDLS_BUNDLE

Audio oversampling clock can be continuously outputted from CLKO pin,

as it is done on Sabre schematic spf-27392, AUD_MCLK, i.MX6_SABRE_SDP_DESIGNFILES .

and It can be configured in linux/../mach-imx/clk-imx6q.c

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

----------------------------------------------------------------------------------------------------------------------- !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thanks for your reply. I agree from your point.

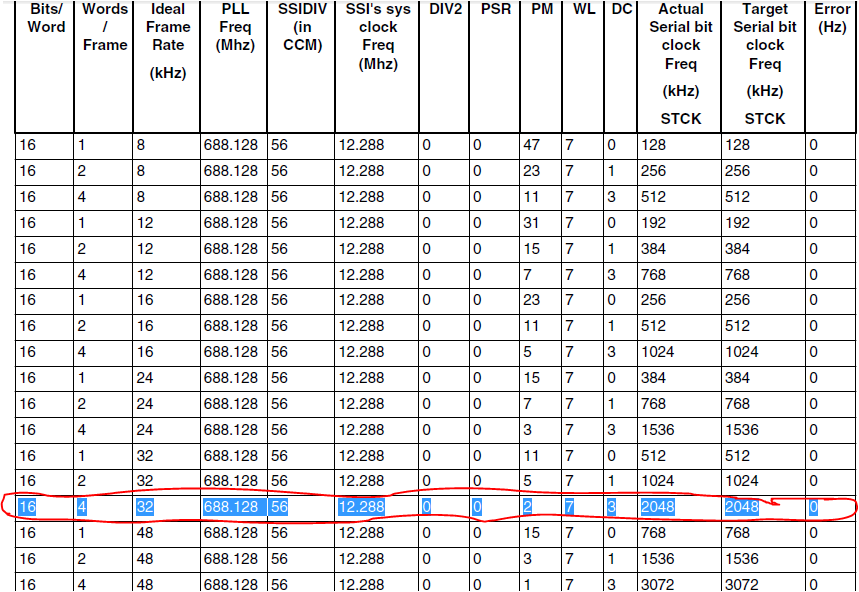

We are modifying the SSI2_SRCCR register with the below mentioned red marked values, Here we are getting 32 Khz of Frame Sync signal which is correct as per thebelow table. But can it be possible some how to get the 2.048Mhz of STCK with 8KHz of Frame Sync?

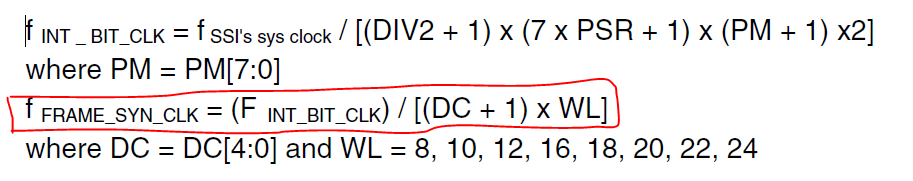

I tired to calculate the Frame sync frequency with this formula by putting WL = 7(16), DC= 15 , DIV2=0, PSR=0 and PM=2 with 2.048Mhz of STCK, but, Did not get any success.

Could you please suggest any solution on this?

Thanks

Sumit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sumit,

How did you modify SSI2_SRCCR register ? Is there any specific file where it can be modified? I am using linux kernel 3.14.1 on my custom board based on imx6q.

Thanks,

Sumish

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Even after modifying the SSI2.SRCCR register, what are the next steps to be taken to up the PCM port? I am using the Silicon Labs SLIC IC Si3228x. I want to use the PCM interface independently even though there is ISI mode (PCM+SPI or GCI) offered in Si3228x.

PSClk is 512 kHz and FSync is 8kHz and the codec data to be sent is 16-bit Linear. Another DAI link is already present, as the alsa driver in the Linux system (3.14 jethro on iMx6q) is used to get data from SGTL5000 chip. The FSync generated internally from the iMx processor is not consistent for future clock cycles, so the FSync is given from the FPGA clock oscillator having a smaller duty cycle.

Best,

Abhijeet

BitMapper

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sumit,

did you ever get a solution for this ?

I have a similar situation with a SiLabs SLIC and I want to generate 2.048MHz clock and 8KHz FSync.

Any help would be welcome.

Regards,

Richard.