- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Flexspi2 is not working

Hello,

I have two serial nor flash chips mounted on my board, which is based on i.mxrt1062.

One flash uses flexspi1 and another uses flexspi2.

I tried running the sdk example project for flexspi driver. It works for flexspi1. It doesn't work for flexspi2.

(SDK_2.4.0_EVK-MIMXRT1060_IAR\boards\evkmimxrt1060\driver_examples\flexspi\nor)

I have done the necessary changes in pin_mux.

I have done the following changes in the flexspi configuration,

#define EXAMPLE_FLEXSPI FLEXSPI2

#define FLASH_SIZE 0x2000 /* 64Mb/KByte */

#define EXAMPLE_FLEXSPI_AMBA_BASE FlexSPI2_AMBA_BASE

#define FLASH_PAGE_SIZE 256

#define EXAMPLE_SECTOR 1

#define SECTOR_SIZE 0x1000 * 14/* 4K */

#define EXAMPLE_FLEXSPI_CLOCK kCLOCK_FlexSpi2

I am using kFLEXSPI_PortB1.

Please advise if I'm missing some configuration.

Regards,

Rohit

Hi Rohit,

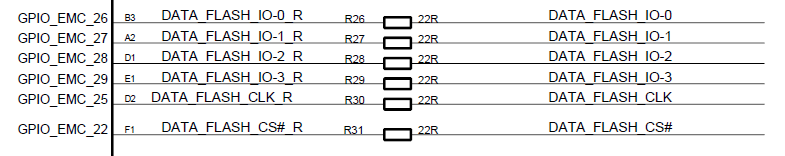

Could you please also share the flexspi2 schematic connections with the external flash chip.

Please also share the pinmux.c modification code, I need to check it.

Waiting for your updated information.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Kerry,

Now I have changed the port to kFLEXSPI_PortA2.

PSB, for the schematic and mux.

void BOARD_InitPins(void) {

CLOCK_EnableClock(kCLOCK_Iomuxc); /* iomuxc clock (iomuxc_clk_enable): 0x03u */

IOMUXC_SetPinMux(

IOMUXC_GPIO_AD_B0_00_GPIO1_IO00, /* GPIO_AD_B0_00 is configured as GPIO1_IO00 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_AD_B0_12_LPUART1_TX, /* GPIO_AD_B0_12 is configured as LPUART1_TX */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_AD_B0_13_LPUART1_RX, /* GPIO_AD_B0_13 is configured as LPUART1_RX */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_AD_B1_02_GPIO1_IO18, /* GPIO_AD_B1_02 is configured as GPIO1_IO18 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_AD_B1_03_GPIO1_IO19, /* GPIO_AD_B1_03 is configured as GPIO1_IO19 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_AD_B1_09_GPIO1_IO25, /* GPIO_AD_B1_09 is configured as GPIO1_IO25 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B0_05_GPIO2_IO05, /* GPIO_B0_05 is configured as GPIO2_IO05 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B0_06_GPIO2_IO06, /* GPIO_B0_06 is configured as GPIO2_IO06 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B0_07_GPIO2_IO07, /* GPIO_B0_07 is configured as GPIO2_IO07 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B0_08_GPIO2_IO08, /* GPIO_B0_08 is configured as GPIO2_IO08 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B0_11_GPIO2_IO11, /* GPIO_B0_11 is configured as GPIO2_IO11 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B1_00_LPUART4_TX, /* GPIO_B1_00 is configured as LPUART4_TX */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B1_01_LPUART4_RX, /* GPIO_B1_01 is configured as LPUART4_RX */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B1_04_LPSPI4_PCS0, /* GPIO_B1_04 is configured as LPSPI4_PCS0 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B1_05_LPSPI4_SDI, /* GPIO_B1_05 is configured as LPSPI4_SDI */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B1_06_LPSPI4_SDO, /* GPIO_B1_06 is configured as LPSPI4_SDO */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B1_07_LPSPI4_SCK, /* GPIO_B1_07 is configured as LPSPI4_SCK */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_B1_08_GPIO2_IO24, /* GPIO_B1_08 is configured as GPIO2_IO24 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_01_GPIO4_IO01, /* GPIO_EMC_01 is configured as GPIO4_IO01 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_04_GPIO4_IO04, /* GPIO_EMC_04 is configured as GPIO4_IO04 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_09_GPIO4_IO09, /* GPIO_EMC_09 is configured as GPIO4_IO09 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_10_GPIO4_IO10, /* GPIO_EMC_10 is configured as GPIO4_IO10 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_12_GPIO4_IO12, /* GPIO_EMC_12 is configured as GPIO4_IO12 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_13_LPUART3_TX, /* GPIO_EMC_13 is configured as LPUART3_TX */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_14_LPUART3_RX, /* GPIO_EMC_14 is configured as LPUART3_RX */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_15_GPIO4_IO15, /* GPIO_EMC_15 is configured as GPIO4_IO15 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_16_GPIO4_IO16, /* GPIO_EMC_16 is configured as GPIO4_IO16 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_17_GPIO4_IO17, /* GPIO_EMC_17 is configured as GPIO4_IO17 */

0U); /* Software Input On Field: Input Path is determined by functionality */

#if 1

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_22_FLEXSPI2_A_SS1_B, /* GPIO_EMC_22 is configured as FLEXSPI2_A_SS1_B */

0U); /* Software Input On Field: Input Path is determined by functionality */

#else

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_24_FLEXSPI2_A_SS0_B, /* GPIO_EMC_22 is configured as FLEXSPI2_A_SS1_B */

0U); /* Software Input On Field: Input Path is determined by functionality */

#endif

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_23_GPIO4_IO23, /* GPIO_EMC_23 is configured as GPIO4_IO23 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_25_FLEXSPI2_A_SCLK, /* GPIO_EMC_25 is configured as FLEXSPI2_A_SCLK */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_26_FLEXSPI2_A_DATA00, /* GPIO_EMC_26 is configured as FLEXSPI2_A_DATA00 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_27_FLEXSPI2_A_DATA01, /* GPIO_EMC_27 is configured as FLEXSPI2_A_DATA01 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_28_FLEXSPI2_A_DATA02, /* GPIO_EMC_28 is configured as FLEXSPI2_A_DATA02 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_29_FLEXSPI2_A_DATA03, /* GPIO_EMC_29 is configured as FLEXSPI2_A_DATA03 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_30_GPIO4_IO30, /* GPIO_EMC_30 is configured as GPIO4_IO30 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_31_GPIO4_IO31, /* GPIO_EMC_31 is configured as GPIO4_IO31 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_33_GPIO3_IO19, /* GPIO_EMC_33 is configured as GPIO3_IO19 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_36_GPIO3_IO22, /* GPIO_EMC_36 is configured as GPIO3_IO22 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_39_GPIO3_IO25, /* GPIO_EMC_39 is configured as GPIO3_IO25 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_40_GPIO3_IO26, /* GPIO_EMC_40 is configured as GPIO3_IO26 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_EMC_41_GPIO3_IO27, /* GPIO_EMC_41 is configured as GPIO3_IO27 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_SD_B0_02_GPIO3_IO14, /* GPIO_SD_B0_02 is configured as GPIO3_IO14 */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_SD_B0_04_LPUART8_TX, /* GPIO_SD_B0_04 is configured as LPUART8_TX */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_SetPinMux(

IOMUXC_GPIO_SD_B0_05_LPUART8_RX, /* GPIO_SD_B0_05 is configured as LPUART8_RX */

0U); /* Software Input On Field: Input Path is determined by functionality */

IOMUXC_GPR->GPR26 = ((IOMUXC_GPR->GPR26 &

(~(IOMUXC_GPR_GPR26_GPIO_MUX1_GPIO_SEL_MASK))) /* Mask bits to zero which are setting */

| IOMUXC_GPR_GPR26_GPIO_MUX1_GPIO_SEL(0x00u) /* GPIO1 and GPIO6 share same IO MUX function, GPIO_MUX1 selects one GPIO function: 0x00u */

);

IOMUXC_GPR->GPR27 = ((IOMUXC_GPR->GPR27 &

(~(IOMUXC_GPR_GPR27_GPIO_MUX2_GPIO_SEL_MASK))) /* Mask bits to zero which are setting */

| IOMUXC_GPR_GPR27_GPIO_MUX2_GPIO_SEL(0x01000800u) /* GPIO2 and GPIO7 share same IO MUX function, GPIO_MUX2 selects one GPIO function: 0x01000800u */

);

IOMUXC_GPR->GPR28 = ((IOMUXC_GPR->GPR28 &

(~(IOMUXC_GPR_GPR28_GPIO_MUX3_GPIO_SEL_MASK))) /* Mask bits to zero which are setting */

| IOMUXC_GPR_GPR28_GPIO_MUX3_GPIO_SEL(0x00u) /* GPIO3 and GPIO8 share same IO MUX function, GPIO_MUX3 selects one GPIO function: 0x00u */

);

IOMUXC_GPR->GPR29 = ((IOMUXC_GPR->GPR29 &

(~(IOMUXC_GPR_GPR29_GPIO_MUX4_GPIO_SEL_MASK))) /* Mask bits to zero which are setting */

| IOMUXC_GPR_GPR29_GPIO_MUX4_GPIO_SEL(0x031000u) /* GPIO4 and GPIO9 share same IO MUX function, GPIO_MUX4 selects one GPIO function: 0x031000u */

);

IOMUXC_SetPinConfig(

IOMUXC_GPIO_AD_B0_12_LPUART1_TX, /* GPIO_AD_B0_12 PAD functional properties : */

0x10B0u); /* Slew Rate Field: Slow Slew Rate

Drive Strength Field: R0/6

Speed Field: medium(100MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Disabled */

IOMUXC_SetPinConfig(

IOMUXC_GPIO_AD_B0_13_LPUART1_RX, /* GPIO_AD_B0_13 PAD functional properties : */

0x10B0u); /* Slew Rate Field: Slow Slew Rate

Drive Strength Field: R0/6

Speed Field: medium(100MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Disabled */

#if 1

IOMUXC_SetPinConfig(

IOMUXC_GPIO_EMC_22_FLEXSPI2_A_SS1_B, /* GPIO_SD_B1_06 PAD functional properties : */

0x10F1u); /* Slew Rate Field: Fast Slew Rate

Drive Strength Field: R0/6

Speed Field: max(200MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Disabled */

#else

IOMUXC_SetPinConfig(

IOMUXC_GPIO_EMC_24_FLEXSPI2_A_SS0_B, /* GPIO_SD_B1_06 PAD functional properties : */

0x10F1u); /* Slew Rate Field: Fast Slew Rate

Drive Strength Field: R0/6

Speed Field: max(200MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Disabled */

#endif

IOMUXC_SetPinConfig(

IOMUXC_GPIO_EMC_25_FLEXSPI2_A_SCLK, /* GPIO_SD_B1_07 PAD functional properties : */

0x10F1u); /* Slew Rate Field: Fast Slew Rate

Drive Strength Field: R0/6

Speed Field: max(200MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Disabled */

IOMUXC_SetPinConfig(

IOMUXC_GPIO_EMC_26_FLEXSPI2_A_DATA00, /* GPIO_SD_B1_08 PAD functional properties : */

0x10F1u); /* Slew Rate Field: Fast Slew Rate

Drive Strength Field: R0/6

Speed Field: max(200MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Disabled */

IOMUXC_SetPinConfig(

IOMUXC_GPIO_EMC_27_FLEXSPI2_A_DATA01, /* GPIO_SD_B1_09 PAD functional properties : */

0x10F1u); /* Slew Rate Field: Fast Slew Rate

Drive Strength Field: R0/6

Speed Field: max(200MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Disabled */

IOMUXC_SetPinConfig(

IOMUXC_GPIO_EMC_28_FLEXSPI2_A_DATA02, /* GPIO_SD_B1_10 PAD functional properties : */

0x10F1u); /* Slew Rate Field: Fast Slew Rate

Drive Strength Field: R0/6

Speed Field: max(200MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Disabled */

IOMUXC_SetPinConfig(

IOMUXC_GPIO_EMC_29_FLEXSPI2_A_DATA03, /* GPIO_SD_B1_11 PAD functional properties : */

0x10F1u); /* Slew Rate Field: Fast Slew Rate

Drive Strength Field: R0/6

Speed Field: max(200MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Disabled */

IOMUXC_SetPinConfig(

IOMUXC_GPIO_AD_B1_03_GPIO1_IO19, /* GPIO_AD_B1_01 PAD functional properties : */

0x10B0u); /* Slew Rate Field: Slow Slew Rate

Drive Strength Field: R0/6

Speed Field: medium(100MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Disabled */

IOMUXC_SetPinConfig(

IOMUXC_GPIO_AD_B1_02_GPIO1_IO18, /* GPIO_AD_B1_01 PAD functional properties : */

0x10B0u); /* Slew Rate Field: Slow Slew Rate

Drive Strength Field: R0/6

Speed Field: medium(100MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Disabled */

}

Regards,

Rohit

Hi Robit,

What's the external nor flash you are using?

Do you mean use the same nor flash, when connect to flexspi1, it works OK, when change the connection to flexspi2, it can't work?

What the board you are testing it? official MIMXRT1060-EVK or your own designed board?

Can you reproduce the problem on official MIMXRT1060-EVK board? Then I can help you to test it.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Kerry,

It is working now after reducing the clock frequency and changing the read sample source.

Thank you very much for your time.

Regards,

Rohit

Hi Robit Ballurgi,

Thank you for your updated information.

And it's very good to hear you make it work.

If you have the other question in the future, welcome to create the new question post.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------