- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Ethernet in External SDRAM Help

Ethernet in External SDRAM Help

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Ethernet in External SDRAM Help

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am working on a project which involves using the Ethernet in external SDRAM. I am using Keilv5 Pro edition with a custom board based off the MIMXRT1050 demo board.

I used the Keil network demo project to test the Ethernet in QSPI flash and it works fine. When I try to use the Ethernet in SDRAM, it does not work. It appears that the Ethernet is not being initialized correctly. The Keil network configuration involves using RTOS2. I need all the project code to be stored and executed in external SDRAM.

I am having the same issue on the MIMXRT1050 demo board in which the network Ethernet works when run through QSPI flash but when I try the same thing in external RAM, it does not work. I believe it has to do with the RTOS memory being used or memory speed differences between the QSPI flash and SDRAM.

Is there something that needs to be set up or changed when using the Ethernet in external SDRAM?

Best,

Kamal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Sorry I don't have knowledge about RTOS RTX5 .

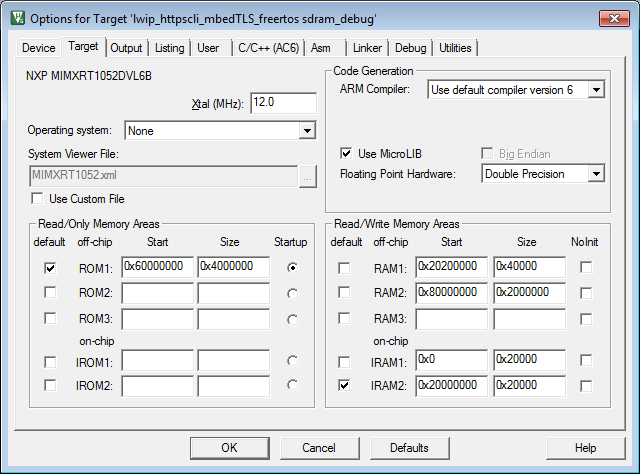

Please also compare the options for the Target

Regards

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kamal:

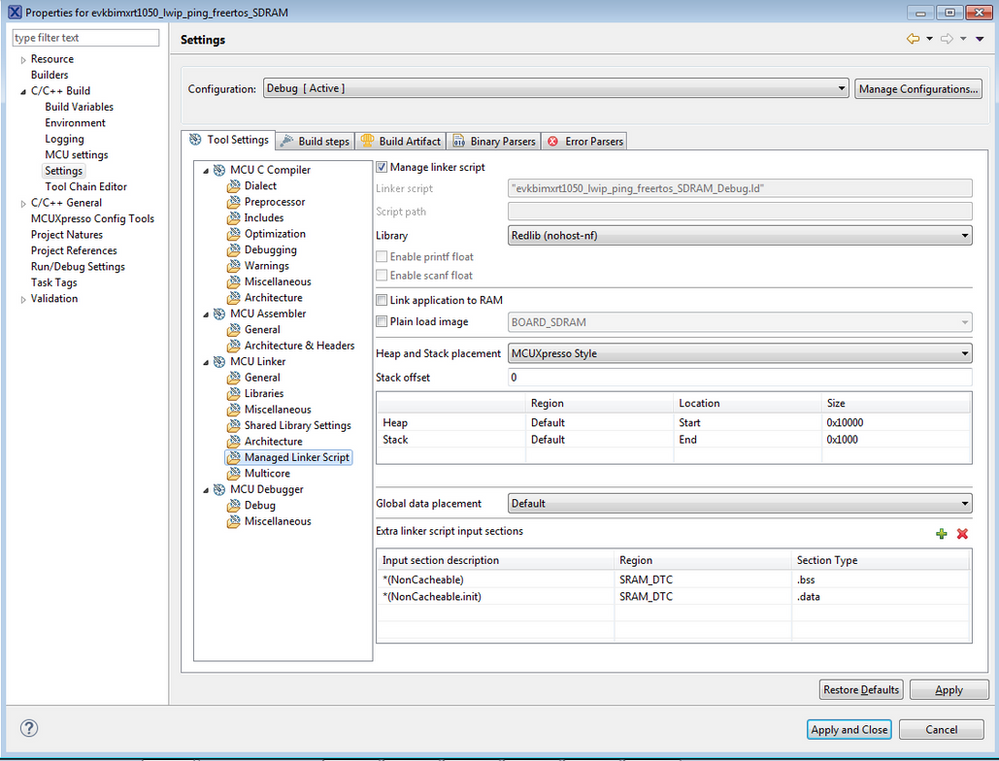

If you are using external SDRAM as your main RAM, for LwIP I would suggest you put some key data structures to SRAM_DTC or other non-cacheable region.

ENET buffers need to store in SRAM_DTC

Original definition:(enet_ethernetif_kinetis.c)

SDK_ALIGN(static rx_buffer_t rxDataBuff_0[ENET_RXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

SDK_ALIGN(static tx_buffer_t txDataBuff_0[ENET_TXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

Change to:

AT_NONCACHEABLE_SECTION_ALIGN(static rx_buffer_t rxDataBuff_0[ENET_RXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

AT_NONCACHEABLE_SECTION_ALIGN(static tx_buffer_t txDataBuff_0[ENET_TXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

I hope this helps.

Regards

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thanks for your helpful information. I am currently using Keilv5 IDE to write code but I did go into MCUXpresso to look at what you were talking about. I don't think that is my issue. I believe the SDRAM is running too fast which is causing errors with hardware. How can I adjust the SDRAM to run at the same speed as the QSPI Flash?

I have code to run a stepper motor from Flash. When I moved the same code to SDRAM, the stepper only worked correctly when I added a 500 nanosecond delay in between steps. I feel the same issue may be occurring with the Ethernet, in which the Ethernet is not being initialized correctly due to the SDRAM clock speed.

I know the code is working at the current Flash speed so if I configure the SDRAM to run at the same speed, I believe it may solve my issues. Is the correct way to change the SDRAM main clock speed done when initializing the SDRAM from Flash or can adjusting the SDRAM clock be completed in SDRAM code?

Is there any example of Ethernet running in external SDRAM or can one be created and sent to me?

Best,

Kamal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

The non-cacheable region can be in SDRAM, or in SRAM_DTC.

There is a demo with LWIP in SDRAM.

Please refer to

SDK_2.7.0_EVKB-IMXRT1050\boards\evkbimxrt1050\lwip_examples\lwip_httpscli_mbedTLS\freertos\mdkI hope it helps.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @danielchen,

I am having a similar problem while trying to run LWIP from SDRAM. I do have a noncacaheable section in the linker:

MEMORY

{

/* Define each memory region */

BOARD_FLASH (rx) : ORIGIN = 0x60000000, LENGTH = 0x800000 /* 8M bytes (alias Flash) */

SRAM_DTC (rwx) : ORIGIN = 0x20000000, LENGTH = 0x20000 /* 128K bytes (alias RAM) */

SRAM_ITC (rwx) : ORIGIN = 0x0, LENGTH = 0x20000 /* 128K bytes (alias RAM2) */

SRAM_OC (rwx) : ORIGIN = 0x20200000, LENGTH = 0xc0000 /* 768K bytes (alias RAM3) */

BOARD_SDRAM (rwx) : ORIGIN = 0x80000000, LENGTH = 0x1000000 /* 16M bytes (alias RAM4) */

NCACHE_REGION (rwx) : ORIGIN = 0x81000000, LENGTH = 0x1000000 /* 12M bytes (alias RAM5) */

}

I've replaced the above-mentioned lines in the enet_ethernetif_kinetis.c file :

err_t ethernetif0_init(struct netif *netif)

{

static struct ethernetif ethernetif_0;

AT_NONCACHEABLE_SECTION_ALIGN(static enet_rx_bd_struct_t rxBuffDescrip_0[ENET_RXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

AT_NONCACHEABLE_SECTION_ALIGN(static enet_tx_bd_struct_t txBuffDescrip_0[ENET_TXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

AT_NONCACHEABLE_SECTION_ALIGN(static rx_buffer_t rxDataBuff_0[ENET_RXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

AT_NONCACHEABLE_SECTION_ALIGN(static tx_buffer_t txDataBuff_0[ENET_TXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

ethernetif_0.RxBuffDescrip = &(rxBuffDescrip_0[0]);

ethernetif_0.TxBuffDescrip = &(txBuffDescrip_0[0]);

ethernetif_0.RxDataBuff = &(rxDataBuff_0[0]);

ethernetif_0.TxDataBuff = &(txDataBuff_0[0]);

return ethernetif_init(netif, ðernetif_0, 0U, (ethernetif_config_t *)netif->state);

}

I don't seem to get a hold of what's happening but there I am not receiving anything on the eth interface.

/* DATA section for NCACHE_REGION */

.data_RAM5 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM5 = .) ;

PROVIDE(__start_data_NCACHE_REGION = .) ;

*(.ramfunc.$RAM5)

*(.ramfunc.$NCACHE_REGION)

*(NonCacheable.init)

*(.data.$RAM5)

*(.data.$NCACHE_REGION)

*(.data.$RAM5.*)

*(.data.$NCACHE_REGION.*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM5 = .) ;

PROVIDE(__end_data_NCACHE_REGION = .) ;

} > NCACHE_REGION AT>BOARD_FLASH

/* BSS section for NCACHE_REGION */

.bss_RAM5 : ALIGN(4)

{

PROVIDE(__start_bss_RAM5 = .) ;

PROVIDE(__start_bss_NCACHE_REGION = .) ;

*(NonCacheable)

*(.bss.$RAM5)

*(.bss.$NCACHE_REGION)

*(.bss.$RAM5.*)

*(.bss.$NCACHE_REGION.*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM5 = .) ;

PROVIDE(__end_bss_NCACHE_REGION = .) ;

} > NCACHE_REGION AT> NCACHE_REGION

Can you please help me with this ?

Thank you,

Vlad Dascau

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have looked at the example you recommended and it does work in SDRAM. The problem is my code uses Keil RTX5 RTOS and the working example uses FreeRTOS. I have tried to adjust my code to work with FreeRTOS but I cannot get it to work. I need to use the Keil RTOS RTX5 to be able to access the SMTP functions.

Also, I do not have these lines of code in my Keil RTX5 project:

SDK_ALIGN(static rx_buffer_t rxDataBuff_0[ENET_RXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

SDK_ALIGN(static tx_buffer_t txDataBuff_0[ENET_TXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

Change to:

AT_NONCACHEABLE_SECTION_ALIGN(static rx_buffer_t rxDataBuff_0[ENET_RXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

AT_NONCACHEABLE_SECTION_ALIGN(static tx_buffer_t txDataBuff_0[ENET_TXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

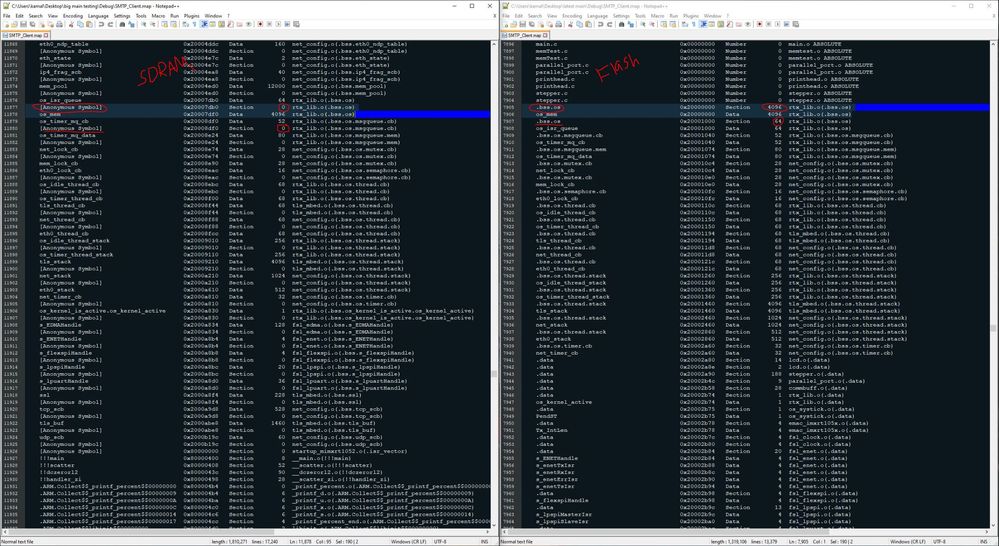

After adjusting my code while keeping Keil RTX5, I created the scatter file that almost matches the working project. In the .map file screenshots, you can see the left side is my non working project and the right side is working. I moved the network files to DTC memory just like the working project. For some reason I am missing the .bss files?

The working project runs in Flash and the scatter files are similar. Do you know how to fix the issue with the missing .bss files?

Best,

Kamal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found that the noncachable buffer fix proposed above did not work for my imxrt1060 project, but what did work is setting `FSL_SDK_ENABLE_DRIVER_CACHE_CONTROL=1` for the project.