- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Code Bus Cache and System Bus Cache

Code Bus Cache and System Bus Cache

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Code Bus Cache and System Bus Cache

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

I am working on i.MX8 . The reference manual of the same talks about Code Bus Cache and system bus cache in multiple places. What exactly are they.? Are they cache for instruction code and data ? Then why are they called Code "Bus" Cache and system "Bus" cache?

Help would be appreciated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

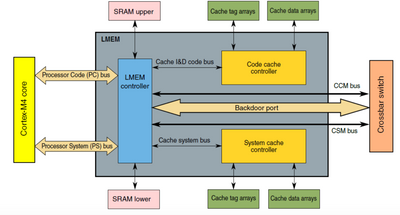

Code Bus and System bus are ARMv7 memory system concepts, in which Code Bus covers 0x0000_0000 - 0x1FFF_FFFF, and System bus covers 0x2000_0000 - 0xFFFF_FFFF.

On iMX8 (M4 as an example) the cache controlled is implemented as LMEM (outer of processor), there are two cache parts, one mapped to Code Bus, the other mapped to System bus.

That's why they are called this way.

But both Code Bus Cache and System Bus cache can cache for instructions and data on its own mapped memory region.

This depends on the memory attributes on each memory region by default or configured by MPU.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The terms Code Bus Cache and System Bus Cache concern the Cortex-M4 processor

(as part of i.MX8), which has "a modified 32-bit Harvard bus architecture. Using a 32-bit

address space, low-order addresses (0x0000_0000 through 0x1FFF_FFFF) use the

Processor Code (PC) bus, and high-order addresses (0x2000_0000 through

0xFFFF_FFFF) use the Processor System (PS) bus. As the bus names imply, normal

operation has code accesses on the PC bus and data accesses on the PS bus.

This device has been augmented with tightly-coupled memories for the PC and PS buses.

The memories include RAMs and caches. These local memories provide zero wait state

access to RAM and cacheable address spaces.

The local memory controller includes four memory controllers and their attached memories:

• SRAM lower (SRAM_L) controller via the PC bus

• SRAM upper (SRAM_U) controller via the PS bus

• Cache memory controller via the PC bus

• Cache memory controller via the PS bus"

Regards,

Yuri.