- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: CTS output strange behave in imx6ul RS485 Mode

CTS output strange behave in imx6ul RS485 Mode

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

CTS output strange behave in imx6ul RS485 Mode

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello, NXP Experts

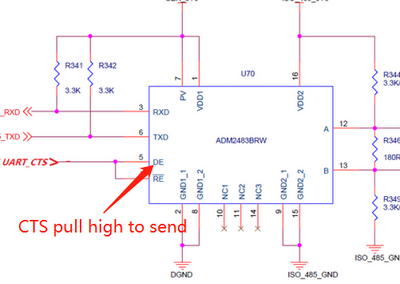

I have success to control RS485 Transceiver's DE/_RE to send/receive data by using CTS as GPIO mode . See below:

&uart4 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart4>;

rts-gpios = <&gpio3 2 GPIO_ACTIVE_HIGH>;

uart-has-rtscts;

linux,rs485-enabled-at-boot-time;

status = "okay";

};

pinctrl_uart4: uart4grp {

fsl,pins = <

MX6UL_PAD_UART4_TX_DATA__UART4_DCE_TX 0x1b0b1

MX6UL_PAD_UART4_RX_DATA__UART4_DCE_RX 0x1b0b1

MX6UL_PAD_LCD_HSYNC__GPIO3_IO02 0x1b0b1 /* CTS pin as gpio*/

>;

};

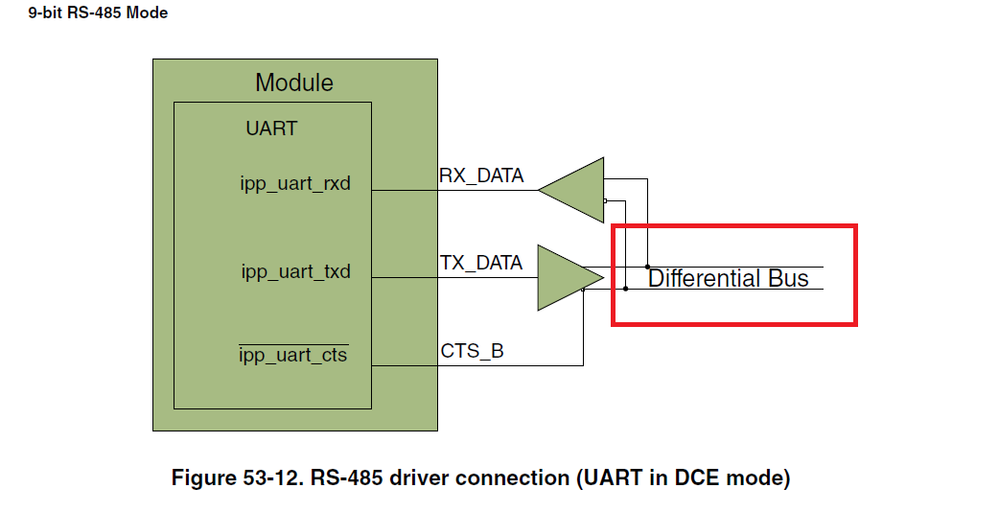

And I noticed there is another way using CTS as UART Controller's CTS_B signal to directly controll RS485 Transceiver's DE/_RE. which also mentioned by @weidong_sun , he said “

---UART_CTS

UART_CTS pin controls IO direction, which may have better performance than GPIO mode, but it also depends on software to determine when TX ends or RX ends. There is always a delay.

”

So now i testing using CTS as UART Controller's CTS_B signal to directly controll RS485 Transceiver's DE/_RE, and modify device tree to:

&uart4 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart4>;rts-gpios = <&gpio3 2 GPIO_ACTIVE_HIGH>;

uart-has-rtscts;

linux,rs485-enabled-at-boot-time;

status = "okay";

};

pinctrl_uart4: uart4grp {

fsl,pins = <

MX6UL_PAD_UART4_TX_DATA__UART4_DCE_TX 0x1b0b1

MX6UL_PAD_UART4_RX_DATA__UART4_DCE_RX 0x1b0b1MX6UL_PAD_LCD_HSYNC__GPIO3_IO02 0x1b0b1 /* CTS pin as gpio*/

MX6UL_PAD_LCD_HSYNC__UART4_DCE_CTS 0x1b0b1 /* dedicated CTS */>;

};

And now i got a strange behave on CTS output.

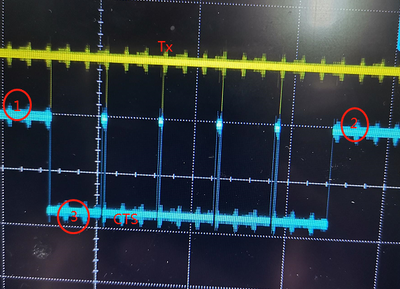

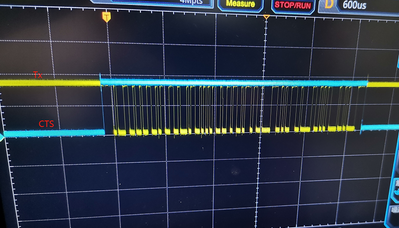

Below i let imx6ul send 5 byte date throught Uart4, i capture the CTS in Oscilloscope:

Strange Behave 1: why CTS held high before Tx datas? (CTS high means Tx in RS485 Transceiver)

Strange Behave 2: why CTS held high after Tx datas? (CTS high means Tx in RS485 Transceiver)

Strange Behave 3: mybe correct.

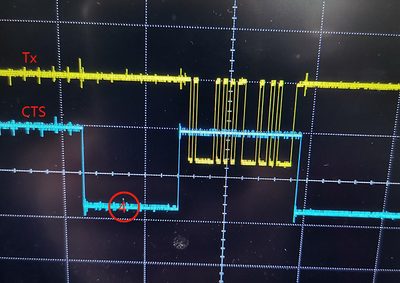

Zoom in the first byte send:

Strange Behave 4: why CTS held low a period before assert(set high) CTS to send data.

Any help are appreciated. Thank you in advance.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

If you read the RS485 spec, you will find RS485 is "half-duplex" communication.

only receive or transmit at one time. that is why need control the direction.

The "before" and "after" is for "receiving".

If you read the i.MX6UL reference manual, you will find RS485 is "1 bit" differential bus.

BTW, data is the plural form of datum. no word "datas" in English.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello, SUN

Thanks for your quick reply.

My confusion is still.

--> The "before" and "after" is for "receiving".

I think "before" and "after" should be low to receive default.

--> BTW, data is the plural form of datum. no word "datas" in English.

Please forgive my poor English.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes.

That is your waveform.

CTS high has data on tx.

Have you sent date to i.MX6UL? and you should measure the waveform on RX pin of i.MX6UL.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

您好,SUN

感谢您的解答。

我理解您说的RS485信号为差分单工。

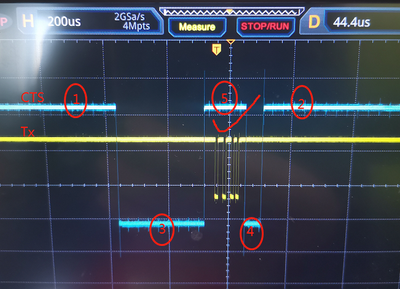

我Post里的图形均为imx6ul发送数据时的波形。(使用的是imx6的UART控制器的CTS功能来控制RS485的收发)

我怕我问题描述不清楚,这里重复一次。我的困惑为以下三点:

1. 在Tx发送数据前和Tx发完数据后,CTS为什么电平会为High(如我图一中的①和②)。

我理解收发控制信号只有在TX真正发送数据时才可以是High,其它时间应该为Low。

2. 每个字节数据发送前为什么CTS会有一小段的拉低过程(如我图三中的④)。

3. 每个字节数据发送后为什么CTS会有一小段的拉低过程(如我图二中的③)。

FYI:

以下是我以GPIO mode方式使用imx6的CTS引脚来控制时的RS485的收发的波形:

你可以看到CTS默认是为低电平的,只有在Tx发送数据时(前)才拉高,发送完后又会回到低电平。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

suggest you can use 0x33 data to make the waveform easy to analyze.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

您好, @BiyongSUN

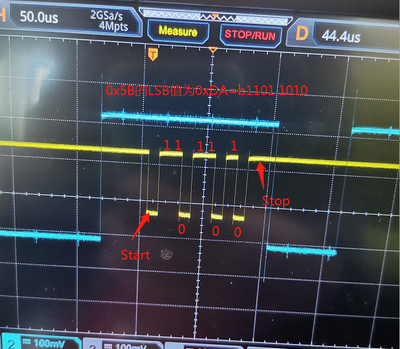

我使用串口发送了一个字节0x5B(LSB为0XDA),波形如下:

(黄色为Tx,蓝色为CTS)

如上图Tx数据波形没有问题。

但是CTS我觉得有问题,如下图:

(下图CTS除了⑤是正常)

问题:

1. 在Tx发送数据前和Tx发完数据后,为什么CTS电平会为High?可否配置为低电平?(如上图的①和②)。

因为RS485的收发控制信号DE/_RE输入为Low时才接收数据,如果CTS电平默认为High则一直无法接收收据。

2. 每个字节数据发送前为什么CTS会有一小段的拉低过程(如上图的③)。

3. 每个字节数据发送后为什么CTS会有一小段的拉低过程(如上图的④)

麻烦您详细解答。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

1. 确认一下用的BSP 的版本。主要是确认一下驱动。

2. 确认一下是用的标准的RS485 的编程。

比方 是用的这些结构。

struct serial_rs485 rs485conf;

memset(&rs485conf, 0, sizeof(rs485conf));

rs485conf.flags |= SER_RS485_ENABLED;

rs485conf.flags |= SER_RS485_RTS_ON_SEND;

rs485conf.flags &= ~(SER_RS485_RTS_AFTER_SEND);

3. 确定一下 dts 文件是按照binding guide 写的。