- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: CCM_ANALOG_MISC2 cannot be configured

CCM_ANALOG_MISC2 cannot be configured

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

CCM_ANALOG_MISC2 cannot be configured

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Freescale,

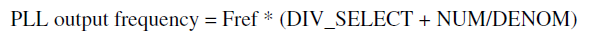

I am trying to use the CCAM_ANALOG_MISC2:AUDIO_DIV_MSB, AUDIO_DIV_LSB so I can divide the PLL4_AUDIO clock (pll4_main_clock) from 688.128MHz to 86.016MHz. I can verify the PLL4_AUDIO is reaching to 688.128MHz when using CCM_ANALOG_PLL_AUDIOn:DIV_SELECT=28, CCM_ANALOG_PLL_AUDIO_NUM=672, CCM_ANALOG_PLL_AUDIO_DENOM=1000. This is following equation with Fref=24MHz:

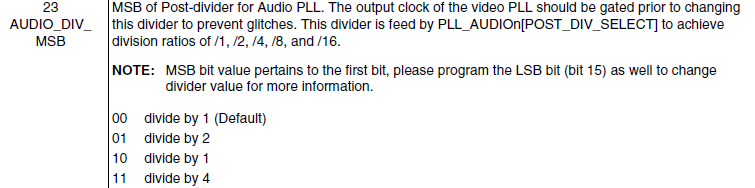

I can also verify the CCM_ANALOG_PLL_AUDIOn:POST_DIV_SELECT=0 (divide by 4) is working to give a pll4_main_clock=172.032MHz. However, when trying to configure CCM_ANALOG_MISC2:AUDIO_DIV_MSB & AUDIO_DIV_LSB to divide by 2:

I do not see the pll4_main_clock=86.016MHz.

My observation is using CCM_CCOSR:CCM_CLKO1 to use PLL4_MAIN_CLK as the source clock with a divider by 1.

I also took note in CCM_ANALOG_MISC2:AUDIO_DIV_MSB where the: output clock of the audio PLL should be "gated" prior to changing this divider to prevent glitches. However when configuring CCM_ANALOG_PLL_AUDIOn:POWERDOWN=1 during ENABLED=1/BYPASS=1, I am unable to get the PLL to enter a DEACTIVE HIGH STATE, which should make the PLL "gated".

I tried with with CCM_ANALOG_PLL_VIDEO and that seems to be working fine.

My order for switching PLL speeds at reset:

1. BYPASS = 0 --> (POWERDOWN will remain = 1 & ENABLE will be = 0)

2. CONFIGURE PLL DIV_SELECT, NUMERATOR, DENOMINATOR, MISC2

3. ENABLE = 1

4. POWERDOWN = 0

5. WAIT WHILE CCM_ANALOG_PLL_AUDIO:LOCK = 1

Is there anything else that I am missing when trying to "gate" PLL4_AUDIO? Or is PLL4_AUDIO is unable to be "gated" since there is no CCGR for pll4_main_clk?

Thanks in advance.

Chris.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi chris

suggest also to try "10" - divide by 1

and use for that i.MX 6Series Platform SDK

and look at EB790 Configuration of Phase Fractional Dividers

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

See this post. https://community.freescale.com/thread/328512?q=PLL4%20AUDIO_DIV

It seems that for iMX6D/Q, "CCM_ANALOG_MISC2n[MSB:LSB]" divider does NOT exist.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am unable to access that link. Can I have privileges to review?

Thank you.

Chris.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Bradley,

Hello. My customer faced the same issue (i.e. He wasn't able to configure the AUDIO_DIV_LSB and MSB).

(Device : i.MX 6Quad)

You said ; CCM_ANALOG_MISC2n[MSB:LSB]" divider does NOT exist.

Really?

I checked the latest reference manual and chip errata today.

But, the related description wasn't found!

Best Regards,

Keita

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Bradley for pointing on that !

Best regards

Igor