- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

About the NAND Row address cycle setting with the SABRE-AI board

Dear all,

We are going to use i.MX6DualLite.

And NAND Boot is used in our system.

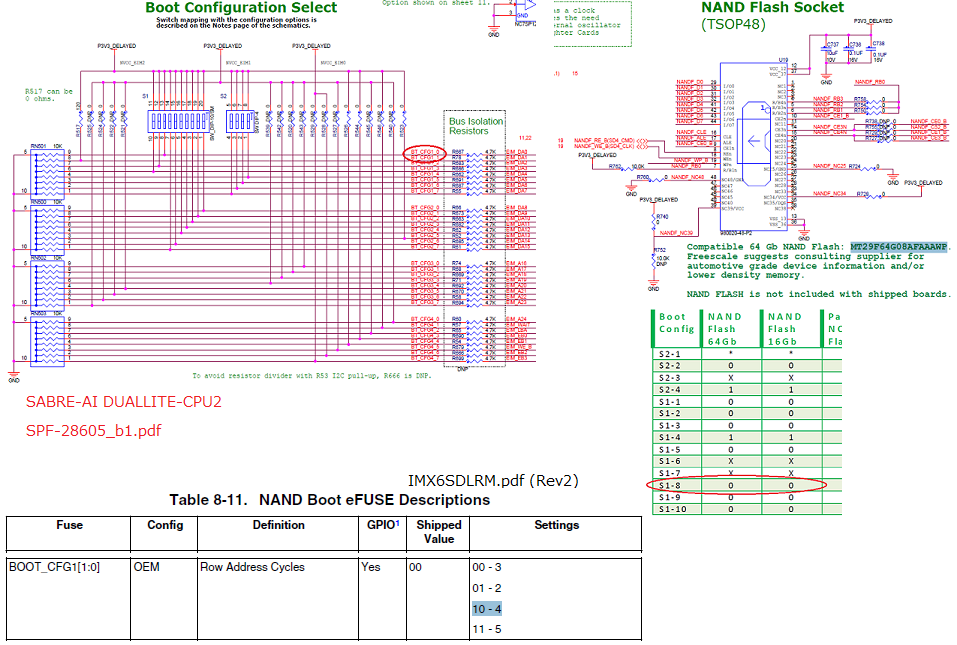

We refer to the schematic of the SABRE-AI board.

- SABRE-AI-DUALLITE-CPU2

=> SPF-28605_b1.pdf

This schematic assumes that MT29F64G08AFAAAWP is used as NAND Flash device.

According to Boot configuration of SABRE-AI, NAND Row address cycle is set to 4.

Boot_CFG1[1:0]=10 (Row Address Cycles is 4)

However, Row address cycle of MT29F64G08AFAAAWP is "3".

<MT29F64G08AFAAAWP Datasheet>

http://pdf.datasheet.directory/datasheets-0/micron_technology/MT29F64G08AFAAAWP_A.pdf

I think that the setting of Row address cycle of SABRE-AI does not match MT29F64G08AFAAAWP.

Would you tell me the reason setting Row address cycle to "4" in SABRE-AI?

Best Regards,

Yuuki Murasato

Actually, setting the Row address cycle number boot parameter larger than the actual Row address cycle number of a NAND Flash device used has no matter for the boot process, since, anyway, all zeros address is latched to a NAND Flash device during initial boot. So, this Row address cycle number setting of 4 has been chosen just for convenience to use single setting for various NAND Flash devices.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------