- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: About special boot mode of eMMC4.3/4.4

About special boot mode of eMMC4.3/4.4

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

About special boot mode of eMMC4.3/4.4

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello community,

I have some basic question about eMMC4.3/4.4 special boot mode.

My understanding of the difference between special boot mode and normal boot mode

of boot ROM function is a memory location to read initial 4 KB of the program image must contain the IVT,

DCD, and the Boot Data structures.

In special boot mode, initial 4KB image read from "BOOT area partition" in eMMC to internal OCRAM.

In normal boot mode, initial 4KB image read from "USER area" in eMMC to internal OCRAM.

1) Is it correct?

If so, how about main BOOT image?

It will read from "User area" in both mode?

2) In "special boot mode", could it use plugin image?

3) How to select Boot partition1 or 2 to use it.

4) Table 8-15. SD/MMC frequencies in Reference Manual of i.MX6QP (IMX6DQPRM.pdf),

Hi-speed of MMC(DDR mode) clock set to 50MHz.

But boot flow from Figure 8-10 to Figure 8-16, it have no timing to set 50MHz.

It have only 20 or 40 MHz setup.

Which timing do eMMC clock set to 50MHz?

Best regards,

Ishii.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Yuri,

Sorry for my late reply.

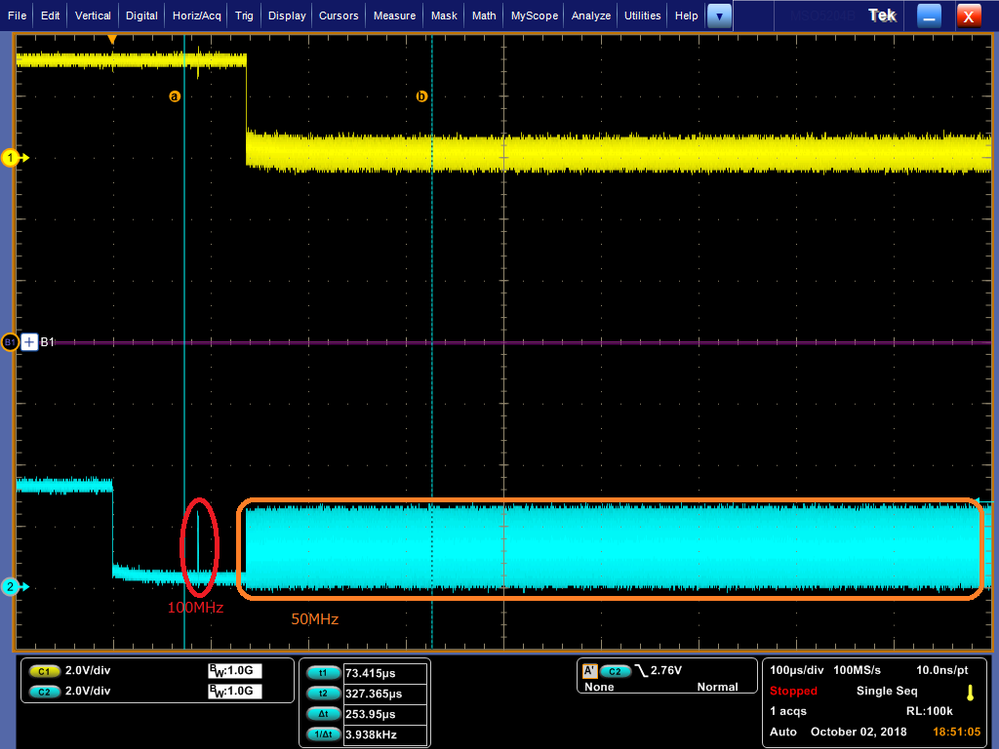

I measured both MMC_CLK(ch2:Cyan) and MMC_CMD(ch1:Yello) with DDR fast boot setting.

(Shorted R712 : BT_CFG2_7 of SABRE-SD to set MMC4.4 8 or 4-bit DDR mode)

After power on, before start to copy 4KB data from BOOTPART1 to OCRAM,

To copy BOOTPART1, MMC_CLK work with 50MHz(Orange).

But befor copy it, MMC_CLK drive with 100MHz(Red).

What is it doing?

Is it a UHSI calibration function?

Best regards,

Ishii.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

The special boot mode means boot mode of the eMMC, when “the master must

keep the CMD line LOW to read all of the boot data”; in such case the slave

recognizes that boot mode is being initiated and starts preparing boot data

internally. The partition from which the master will read the boot data can be selected

in advance using EXT_CSD byte [179], bits [5:3]. The data size that the

master can read during boot operation can be calculated as 128KB ×

BOOT_SIZE_MULT (EXT_CSD byte [226]).”

Please refer to eMMC4.3 (and higher) specs for more details.

Have a great day,

Yuri

------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer

button. Thank you!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Yuri,

Thank you for your quick response.

But what I want to know is how this partition is used in boot ROM.

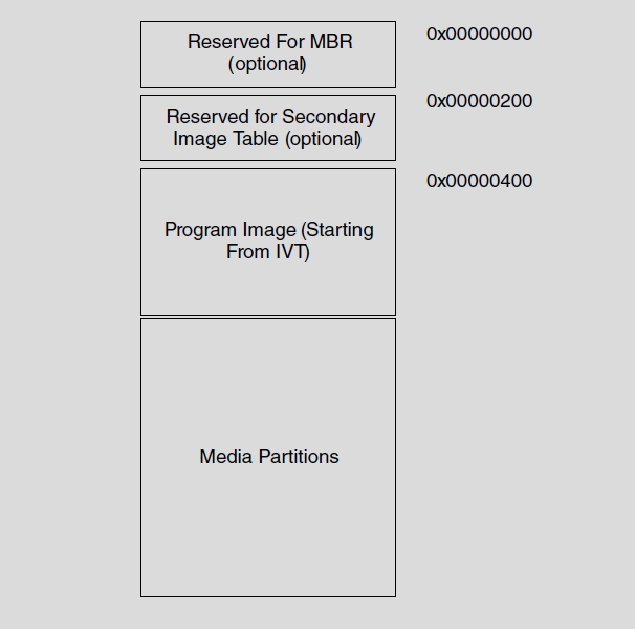

In MMC/SD-Card boot, boot ROM copy 4KB boot image from sector 2 of MMC/SD card to internal RAM.

So user area(main storage) are parted to 4 area.

user area : MBR(sector 0,1) + u-boot(IVT+DCD) + FAT(zImage + .dtb file) + Ext4(Linux file system)

If eMMC4.3(or higher) use as boot device, it can use "Boot area partition" separated from the user area.

I think that it will parted as following.

user area : MBR(sector 0,1) + Ext4(Linux file system)

boot partition : IVT+DCD + zImage + .dtb file

Is it correct?

If so, boot ROM in eMMC boot copy 4KB boot image from boot partition(in eMMC) to internal RAM(in i.MX6).

Is it correct?

Currently, my customer use plugin image, does it use with eMMC4.3(or higher) boot operation?

Best regards,

Ishii.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello, Ishii!

According to Figure 8-17 (Expansion device structures layout) of i.MX 6Dual/6Quad RM, Rev. 4, 09/2017,

IVT, DCD, and the Boot Data structures are located separately (outside of device partitions).

Regards,

Yuri.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Yuri,

Do you mind answering about question 4)?

I think to set 50MHz emmc clock for DDR mode, it is just before to issue a switch command(CMD6)

to change bus width and DDR mode.(Figure 8-11. Expansion device (MMC) boot flow (2 of 6) in IMX6DQPRM rev1)

Is it correct?

Best regards,

Ishii.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Boot ROM uses 40 MHz in the high-speed mode.

~Yuri.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Yuri,

Thank you for your quick response.

In Table 8-15 of IMX6DQPRM_rev1, Hi-speed mode MMC is 40MHz and Hi-speed mode MMC(DDR mode) is 50MHz.

Is this wrong?

Best regards,

Ishii.