- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- ADMA LPUART0 Interrupt Configuration on the iMX8X Module

ADMA LPUART0 Interrupt Configuration on the iMX8X Module

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADMA LPUART0 Interrupt Configuration on the iMX8X Module

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Requirement:

Configure the Rx_Data_Register_Full Interrupt for ADMA LPUART0 on the CM4 core.

Here's what I've tried:

All A35 cores have been disabled via U-Boot, so only the CM4 core is active.

ADMA LPUART0 operates correctly in polling mode for both reading and writing.

Although the interrupt has been configured, it is not triggering.

Questions:

How can this issue be resolved?

Could you please provide an example code for configuring this interrupt? (Note: An example for the CM4 dedicated UART is not needed.)

Is it necessary to configure IRQSTEER for this interrupt? If so, when and where should IRQSTEER be configured? Please include a demonstration code if possible.

Current Code Snippet:

LPUART_EnableInterrupts(ADMA__LPUART0, kLPUART_RxDataRegFullInterruptEnable);

EnableIRQ(ADMA_UART0_INT_IRQn);

NVIC_SetPriority(ADMA_UART0_INT_IRQn, 0x07);

#imx8x #UART_Interrupt

@kerryzhou

Thanks and Regards

Alexxis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Alexxis_04

I hope you are doing very well.

Apologies for the long delay.

It appears, yes, the IRQSTEER should be configured.

Please take a look t the lpuart_edma_transfer.c of SDK 2.9.0:

/* Enable interrupt in irqsteer */

IRQSTEER_Init(IRQSTEER);

IRQSTEER_EnableInterrupt(IRQSTEER, ADMA_UART0_DMA_RX_INT_IRQn);

IRQSTEER_EnableInterrupt(IRQSTEER, ADMA_UART0_DMA_TX_INT_IRQn);

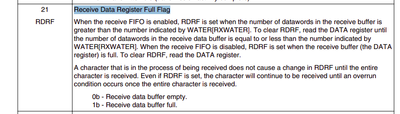

Also, keep in mind that Receive Data Register Full Flag behavior:

So, you can try to disable the FIFO or set the Watermark to 0.

I hope this information can helps to you.

Best regards,

Salas.