- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MXプロセッサ

- :

- i.MXプロセッサ ナレッジベース

- :

- System Controller Firmware 101 - Power management service

System Controller Firmware 101 - Power management service

- RSS フィードを購読する

- 新着としてマーク

- 既読としてマーク

- ブックマーク

- 購読

- 印刷用ページ

- 不適切なコンテンツを報告

System Controller Firmware 101 - Power management service

System Controller Firmware 101 - Power management service

The System Controller Unit (SCU) is in charge of controlling several features related to power management of the whole system. The

user gets access to the following features through the System Controller Firmware:

- Powering up/down the system,resources and partitions

- Configuring resource clocks

- Reset controls

- Configuring wake-up sources

This document will cover the more commonly used features, for details on the full capabilities of the API please refer to the API document for your device.

Resource Power Control

The SCU is in charge of managing power control to the resources (peripherals) in the SoC.

Attempting to access a resource on the OFF state will result in a bus error or a hang

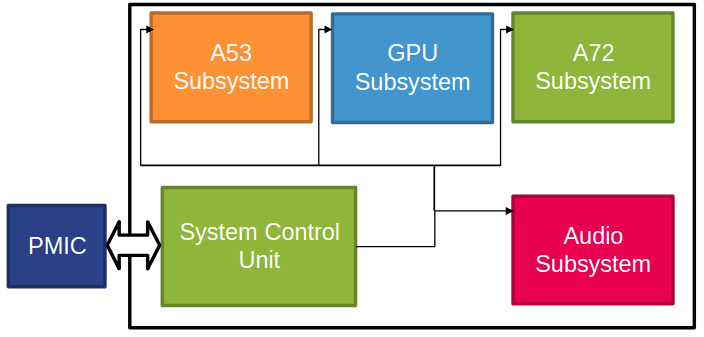

All resources are organized within several subsystems, subsystems group together resources with common functionality. Subsystems are independent of each other and have their own PLLs and power domains, this allows modular control of clocks and power to the resources.

The System Controller Unit has a dedicated I2C channel to interact with the PMIC, this allows dynamic control of some power sources for resources like the GPUs and Cortex-A cores.

The SCU can enable/disable the LDO that supplies power to the GPU for instance and also turn on/off the internal power domains. The mapping of PMIC supplies and resources happens on the board.c (included in the SCFW Porting kit) and it is part of the porting process of the SCFW to new boards.

The function board_get_pmic_info is where the mapping of resources to supplies happen, see:

/*--------------------------------------------------------------------------*/

/* Get the pmic ids and switchers connected to SS.

*/

/*--------------------------------------------------------------------------*/

static void board_get_pmic_info(sc_sub_t ss,pmic_id_t *pmic_id,

uint32_t *pmic_reg, uint8_t *num_regs)

{

/* Map SS/PD to PMIC switch */

switch (ss)

{

case SC_SUBSYS_A53 :

pmic_init();

{/* PF8100_dual Card */

pmic_id[0] = PMIC_0_ADDR;

pmic_reg[0] = PF8100_SW5;

*num_regs = 1U;

}

break;

case SC_SUBSYS_A72 :

pmic_init();

{/* PF8100_dual Card */

pmic_id[0] = PMIC_0_ADDR;

pmic_reg[0] = PF8100_SW3;

pmic_id[1] = PMIC_0_ADDR;

pmic_reg[1] = PF8100_SW4;

*num_regs = 2U;

}

break;

case SC_SUBSYS_GPU_0 :

pmic_init();

{/* PF8100_dual Card */

pmic_id[0] = PMIC_1_ADDR;

pmic_reg[0] = PF8100_SW1;

pmic_id[1] = PMIC_1_ADDR;

pmic_reg[1] = PF8100_SW2;

*num_regs = 2U;

}

break;

case SC_SUBSYS_GPU_1 :

pmic_init();

{/* PF8100_dual Card */

pmic_id[0] = PMIC_1_ADDR;

pmic_reg[0] = PF8100_SW3;

pmic_id[1] = PMIC_1_ADDR;

pmic_reg[1] = PF8100_SW4;

*num_regs = 2U;

}

break;

default :

; /* Intentional empty default */

break;

}

}Only some subsystems have their own dedicated external power supplies, in the example above A cores and GPUs are the only ones with a dedicated external power supplies. Most of the other subsystems are powered from the main power supply and power gating happens internally, each subsystem contains different power domains that can be turned on/off to manage power consumption.

The SCFW API used to power on/off resources is the following:

sc_err_t sc_pm_set_resource_power_mode (sc_ipc_t ipc, sc_rsrc_t resource, sc_pm_power_mode_t mode)Where:

ipc - is the interprocessor communication channel used to communicate with the SCU (obtained by calling sc_ipc_open).

resource - is the resource that will have the power mode change

mode - is the power mode to change to

The available power mode options are the following:

| Power mode | Voltage | Clocks |

|---|---|---|

| SC_PM_PW_MODE_OFF | OFF | All clocks off |

| SC_PM_PW_MODE_STBY | ON | All clocks off |

| SC_PM_PW_MODE_LP | ON | PLLs off resource running from XTAL |

| SC_PM_PW_MODE_ON | ON | PLLs on |

In order to be able to access a resource it must be at least on SC_PM_PW_MODE_LP mode, since that mode has the resource voltage on and the clock is supplied by the 24MHz crystal.

For more details please refer to the SCFW API document.

Clocks Configuration

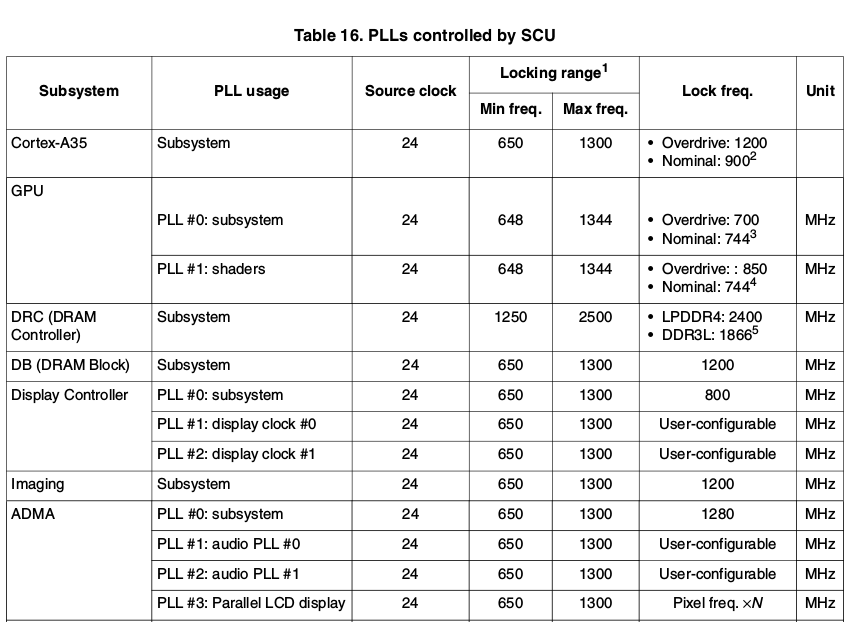

As in the power management case, clocks are also organized in a distributed manner within the device. Each subsystem has it's own PLLs and all of them are clocked by the 24MHz crystal. The number of PLLs in each subsystem varies between all subsystems.

To see how many PLLs are within a subsystem please refer to the datasheet of the device you are interested on.

For instance on the datasheet of the i.MX8QXP on table 16 in Chapter 4.3.1:

It can be seen that the GPU subsystem contains two PLLs, the ADMA subsystem contains 4 PLLs, Display Controller 3, etc...

The SCFW API used to configure a clock is the following:

sc_err_t sc_pm_set_clock_rate (

sc_ipc_t ipc,

sc_rsrc_t resource,

sc_pm_clk_t clk,

sc_pm_clock_rate_t ∗ rate )Where:

ipc - is the interprocessor communication channel used to communicate with the SCU (obtained by calling sc_ipc_open).

resource - is the resource that will have the clock rate change

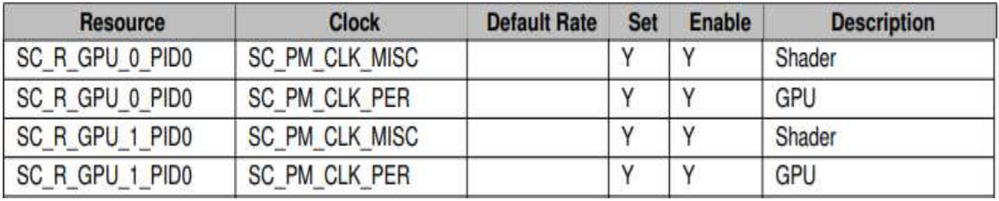

clk - is the clock to set the rate to (each resource can have different clocks associated with it for instance the GPU resource has a clock associated for its shader and another for the GPU, this parameter is used to identify the clock)

rate - this contains the desired clock rate, the SCFW will try to match the provided rate if not possible it will then set the closest possible value and return the value that was actually configured.

To identify the clk that needs to be passed, please refer to the SCFW API chapter called "Clock List"

That chapter contains a table with all the different clocks that are configurable by the SCFW, in the case of the GPUs for instance to select the rate for the Shader or GPU, either the SC_PM_CLK_MISC or SC_PM_CLK_PER options would have to be selected.

Set=Y indicates the clock/PLL is not shared and the rate can be set via sc_pm_set_clock_rate().

Enable=Y indicates the clock is not auto gated and must be enabled via sc_pm_clock_enable().

As an example the following snippet configures the GPU_0 shader clock:

sc_clock_rate_t shader_clk=700000000; // 700 MHz

sc_pm_set_clock_rate(ipc, SC_R_GPU_0_PID0, SC_PM_CLK_MISC, &shader_clk);