- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Dear Sir/Madam,

I have a protoype board for VF3x. I am using DS-5 and MQX to test it. Since MQX is prepared for tower kit, the core clock is set to 399 MHz in clocks.init() in init_hw.c file, as below:

// wait to lock pll

while ((Anadig_PLL_LOCK & PLL_LOCKS) != PLL_LOCKS);

// ARM_CLK: SYS_CLK/1 = 396Mhz

// BUS_CLK: ARM_CLK/3 = 132Mhz

// IGP_CLK: BUS_CLK/2 = 66Mhz

// AUDIO_DIV: 73Mhz ??

CCM_CACRR = CCM_CACRR_ARM_CLK_DIV(0) | CCM_CACRR_BUS_CLK_DIV(2) | CCM_CACRR_IPG_CLK_DIV(1) | CCM_CACRR_PLL4_CLK_DIV(7);

There are definitions for the CCM_CACRR_ARM_CLK_DIV() in MVF50GS10MK50.h file as:

#define CCM_CACRR_ARM_CLK_DIV_MASK 0x7u

#define CCM_CACRR_ARM_CLK_DIV_SHIFT 0

#define CCM_CACRR_ARM_CLK_DIV(x) (((uint32_t)(((uint32_t)(x))<<CCM_CACRR_ARM_CLK_DIV_SHIFT))&CCM_CACRR_ARM_CLK_DIV_MASK)

But it is not easy to reach a result from this line for me. How can I set the core frequency to 266 MHz? ( I guess it is the maximum frequency for VF3x)

Thanks and best regards.

Mehmet Ali Ipin

已解决! 转到解答。

Nothe that Im refering to code in twrvf65gs10 but it should be very similar for vf3 or maybe identical

In clocks_init you should have some seeting for the CCM_CCSR like below:

CCM_CCSR = 0x0003FF24;

which set (among other things)

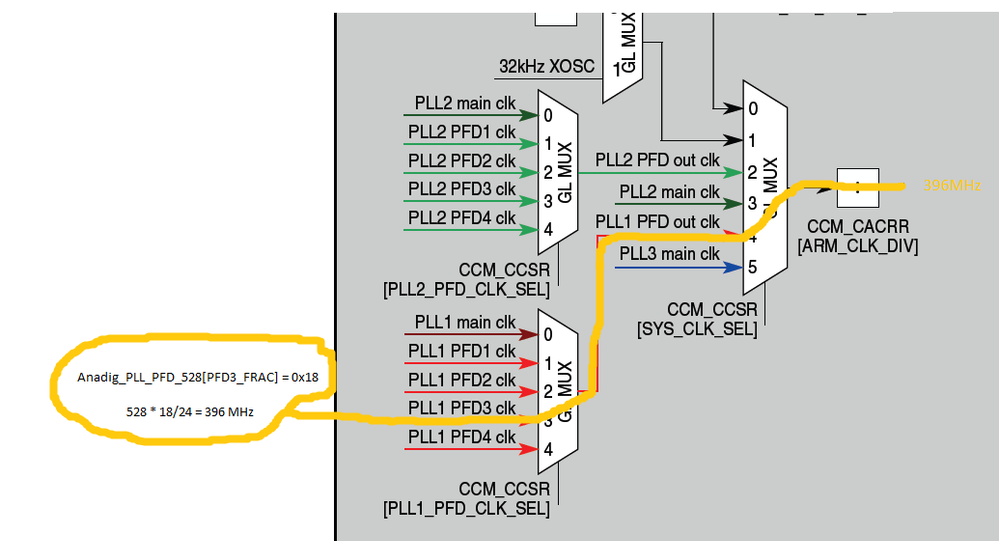

CCM_CCSR[PLL1_PFD_CLK_SEL] = 0x3 ----> PLL1 uses PLL1_PFD3

CCM_CCSR[SYS_CLK_SEL] = 0x4 ----> use PLL1_PFD

The Anadig_PLL_PFD_528 might NOT be set, because using the default RESET values

From Reference Manual the reset value for pfd3_frac is:

Anadig_PLL_PFD_528[PFD3_FRAC] = 0x18 = d24

This is setting the resulting freq = 528 * 18/24 = 396 MHz, through the next path

For getting the 266MHz Frequency at PLL1_PFD3 you need to tweak the value of Anadig_PLL_PFD_528[PFD3_FRAC] close to 266MHz is

Anadig_PLL_PFD_528[PFD3_FRAC] = d36 = 0x24

PLL1_PFD3_freq = 528 * 18 / 36 = 264 Mhz

SYS_CLK = PLL1_PFD3_freq / ARM_CLK_DIV = 264/1 = 264Mhz

You can try to check if there is a better way to get a closer value to 266Mhz.

You need to tweak different values like Anadig_PLL_PFD_528[PFD3_FRAC], Anadig_PLL1_CTRL[DIV_SELECT], CCM_CACRR[ARM_CLK_DIV], etc.

You can try setting a smaller value in the PFD3_FRAC, so PLL1_PFD3 output is a higher frequency and set a higher divisor value in CCM_CACRR[ARM_CLK_DIV].

Nothe that Im refering to code in twrvf65gs10 but it should be very similar for vf3 or maybe identical

In clocks_init you should have some seeting for the CCM_CCSR like below:

CCM_CCSR = 0x0003FF24;

which set (among other things)

CCM_CCSR[PLL1_PFD_CLK_SEL] = 0x3 ----> PLL1 uses PLL1_PFD3

CCM_CCSR[SYS_CLK_SEL] = 0x4 ----> use PLL1_PFD

The Anadig_PLL_PFD_528 might NOT be set, because using the default RESET values

From Reference Manual the reset value for pfd3_frac is:

Anadig_PLL_PFD_528[PFD3_FRAC] = 0x18 = d24

This is setting the resulting freq = 528 * 18/24 = 396 MHz, through the next path

For getting the 266MHz Frequency at PLL1_PFD3 you need to tweak the value of Anadig_PLL_PFD_528[PFD3_FRAC] close to 266MHz is

Anadig_PLL_PFD_528[PFD3_FRAC] = d36 = 0x24

PLL1_PFD3_freq = 528 * 18 / 36 = 264 Mhz

SYS_CLK = PLL1_PFD3_freq / ARM_CLK_DIV = 264/1 = 264Mhz

You can try to check if there is a better way to get a closer value to 266Mhz.

You need to tweak different values like Anadig_PLL_PFD_528[PFD3_FRAC], Anadig_PLL1_CTRL[DIV_SELECT], CCM_CACRR[ARM_CLK_DIV], etc.

You can try setting a smaller value in the PFD3_FRAC, so PLL1_PFD3 output is a higher frequency and set a higher divisor value in CCM_CACRR[ARM_CLK_DIV].