- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- Vybrid Processors

- :

- Debugging BSCAN test for Vybrid. Chip doesn't seem to respond correctly with this BSDL file

Debugging BSCAN test for Vybrid. Chip doesn't seem to respond correctly with this BSDL file

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I made a boundaryscan project for our Vybrid module with the "Cascon" tools from Göpel electronic.

The "infrastructure" test, which reads the Vybrid ID and checks the JTAG scanchain works fine.

But every other test I try fails, because none of the Vybrid pins seems to be driveable. The BSDL file contains no compliance pattern which means that there are no conditions which have to met to enable boundaryscan. The Vybrid CPU has two "test" pins (#T3 and #T1). Maybe I have to use these pins in some way (they are tied to GND)? There is no information about that in the datasheets.

Here are some information about the environment I use:

- Cascon 4.6.2b

- BSDL File VYBRID_364_F.bsdl Version 5

- Vybrid CPU marking "PVF65GS10CMK40 TEST REV B1" ( also tried step C3 )

Any help to get the boundaryscan test running is welcome :-)

Regards

Eric

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eric,

I checked with the design team, there are no special requirements to enable BSDL, expectation is the supplied BSDL file should work. Can you create or generate a log file with perhaps some more detail on the sequence of events you are seeing, this may help us debug what is happening?

Thanks

Ross

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ross,

I wrote two small CasLan based example programs (CasLan is the programming language of Cascon, Göpels boundaryscan tool).

I hope that I could explain the problem with these examples :-)

The hardware I use connects a CION chip U5_TH027 (this is a ASIC developed by Göpel which has good boundaryscan capabilities) to the Vybrid CPU U4_PCM052.

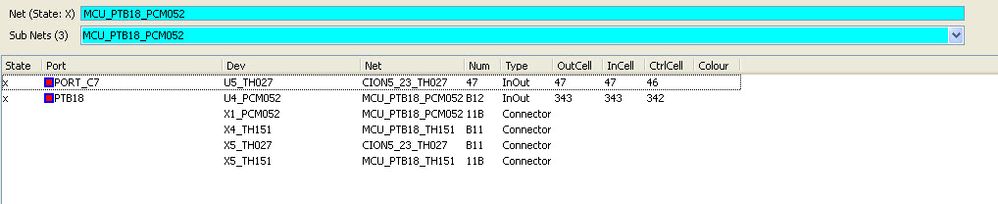

The picture shows the net based on the schematic netlist.

U5_TH027 Pin "PORT_C7" ------ connector -------- connector ---------- U4_PCM052 Pin "PTB18"

Measuring the net with my Oscilloscope I could see that example 1 drives the net HIGH successfully.

Executing example two leads to no changes on the scope, but it also should drive the net HIGH. This is the problem I am talking about.

There is one wired additional information: executing the last DRSHIFT in example two causes the Vybrid RESETb pin to drive a LOW.

The scanchain is still working so it might not be a problem.

(There is a short "init sequence" not shown here which brings all ICs into sample mode and configures the used scan router.)

Example 1: drive the Cion Pin

ENABLE (U5_TH027:PORT_C7);

DH (U5_TH027:PORT_C7);

DRSHIFT;

ldi U5_TH027, EXTEST;

IRSHIFT;

DRSHIFT;

Example two: drive the Vybrid Pin.

ENABLE (U4_PCM052:PTB18);

DH (U4_PCM052:PTB18);

DRSHIFT;

ldi U4_PCM052, EXTEST;

IRSHIFT;

DRSHIFT; <-- Vybrid RESETB goes low

Regards Eric

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

RossMcLuckie can you continue with the follow up on this case?