- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

FXOS8700 - sleep INT keeps repeating

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi!

In my app I am trying to setup the VECM and PULSE event for auto-sleep/wake mode.

Without auto-sleep everything works fine.

When setting up auto-sleep I keep getting auto-sleep interrupts even though interrupts are being cleared by the MCU.

ACC sensor setup is:

// put device into standby mode

ACC_Write_Register( FXOS8700CQ_REG_CTRL_REG1, 0x00);

// set full scale range

// XYZ_DATA_CFG => +/-2g range with 0.244mg/LSB

ACC_Write_Register( FXOS8700CQ_REG_XYZ_DATA_CFG, 0x00);

/*! ***************** VECTOR-MOTION DETECTION ********************* */

// A_VECM_THS_MSB, _LSB

// = 0x02B9 => 143 *0.244mg = ~35mg = ~2°, debounce reset when out of trigger

ACC_Write_Register( FXOS8700CQ_REG_A_VECM_THS_MSB, 0x80 | 0x00 );

ACC_Write_Register( FXOS8700CQ_REG_A_VECM_THS_LSB, 0xD6 );

// A_VECM_CNT debounce counter 0x07 * 1/12.5Hz = 540ms

ACC_Write_Register( FXOS8700CQ_REG_A_VECM_CNT, 0x07 )+;

// A_VECM_CFG: event latching enabled, enable acceleration vector magnitude

ACC_Write_Register( FXOS8700CQ_REG_A_VECM_CFG, 0x48 ); //was 0x48

/*! ***************** ENABLE INTERRUPT GENERATION ***************** */

// enable interrupts for the feature using CTRL_REG4: vector + auto-sleep

ACC_Write_Register( FXOS8700CQ_REG_CTRL_REG4, ACC_INT_VECTOR | 0x80 );

// route interrupts to INT1 pin using CTRL_REG5: vector + auto-sleep

ACC_Write_Register( FXOS8700CQ_REG_CTRL_REG5, ACC_INT_VECTOR | 0x80 );

// CTRL_REG2 - set low power/low noise, auto-sleep: enabled

ACC_Write_Register( FXOS8700CQ_REG_CTRL_REG2, 0x09 | 0x04 );

// sleep event function enables: vector

ACC_Write_Register( FXOS8700CQ_REG_CTRL_REG3, 0x04 );

// FIFO setup: no FIFO

ACC_Write_Register( FXOS8700CQ_REG_F_SETUP, 0x00 );

ACC_Write_Register( FXOS8700CQ_REG_ASLP_COUNT, 0x06 );

// CTRL_REG1

// Setup device for acc only mode

// wake and sleep mode ODR setting: 12.5 Hz

ACC_Write_Register( FXOS8700CQ_REG_CTRL_REG1, 0x40 | 0x28 | 0x01 );

For handling the interrupt I read the INT_SOURCE register and decide based on content how to handle the event. If it is an auto-sleep interrupt the MCU simply reads SYSMOD to clear the interrupt.

The order of register reads is:

- INT_SOURCE

- SYSMOD - only if auto-sleep interrupt

The interrupt handling as such works fine according to logs. Also the ACC sensor is indeed going to sleep.

time;int_source;evt;sysmod

1951900 128 sleep event, mode 2

2012020 128 sleep event, mode 2

2092160 128 sleep event, mode 2

2172330 128 sleep event, mode 2

2252470 128 sleep event, mode 2

2332610 128 sleep event, mode 2

2412780 128 sleep event, mode 2

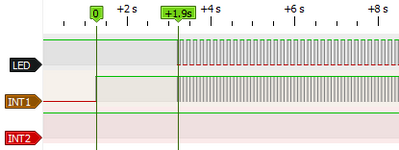

On the scope I see correct behavior at first (going to sleep after 1.9s). Then the INT1 signal fires continuously at the rate of the sleep-ODR (f=12.5Hz, T=80ms).

Am I missing something for clearing the auto-sleep interrupt?

Thanks for input on this!

Cheers

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello JRB,

Thank you for your question.

Please help answer following so that we can help assist you better:

- The advantage of using the auto-wake/sleep is that the system can automatically transition to a higher sample rate (higher current consumption) when needed but spends the majority of the time in the sleep mode (lower current) when the device does not require higher sampling rates. From your CTRL_REG1 configuration it appears that you are configuring both WAKE and SLEEP ODR to 12.5Hz? This won't give any advantage in your application using auto-wake/sleep. I would suggest you to refer to the app note AN4074.

- Please confirm the VECM THS you are configuring (its not very clear from the code snippet you have shared):

// A_VECM_THS_MSB, _LSB

// = 0x02B9 => 143 *0.244mg = ~35mg = ~2°, debounce reset when out of trigger

ACC_Write_Register( FXOS8700CQ_REG_A_VECM_THS_MSB, 0x80 | 0x00 );

ACC_Write_Register( FXOS8700CQ_REG_A_VECM_THS_LSB, 0xD6 );

I see that you are configuring A_VECM_THS_MSB as 0x80 and A_VECM_THS_LSB as 0xD6, that translates A_VECM as 0D6h => 214 * 0.244mg ~= 52mg, which seems a very low threshold. Please confirm whether you want to have VECM THS as ~=52mg as per your application requirements?

- Please specify what is "ACC_INT_VECTOR".

Regards,

Amit.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Amit,

to answer your questions:

- auto-wake/sleep - it is intentional to run at the same sample rate in wake and sleep mode in our application

- VECM threshold - yes, it is intentional to have such a low value. This works well in our application.

- ACC_INT_VECTOR is 0x02, this is equal to int_cfg_a_vecm and int_en_a_vecm in Reg4+5.

Thanks for your support on this!

Cheers