- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- Sensors

- :

- Re: Re: Clearing MMA8652 Interrupts

Clearing MMA8652 Interrupts

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am working with an MMA8652 accelerometer. It generates a transient interrupt (in response to a tap) fine but I am unable to clear it, so it continues to interrupt.

I read the interrupt source register (0x0C), and then the transient source register (0x1E) following the interrupt. Then I re-read the interrupt source register: bit for transient interrupt still set. The datasheet and app notes say that reading the transient source register should clear the interrupt. When I read regs 0x0C and 0x1E they are always 0xFF after the initial interrupt. What am I missing?

Also, the datasheet seems to imply that the VDDIO is tied to VDD. Is this correct?

Harold

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Harold,

Could you please post here the waveforms to review what is going on on the I2C bus?

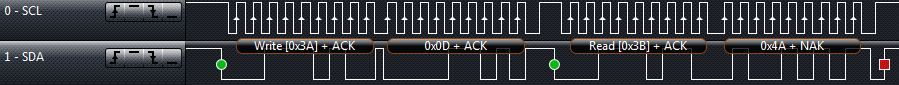

A single byte read e.g. from the WHO_AM_I register 0x0D should look like this:

A common problem with the read operation is sending a stop condition (a low to high transition of SDA while SCL is high) after the second byte (in this case 0x0D). The correct way is to release the SDA line (so that it transitiones to high) before the SCL line goes high.

As for the pull-up resistors, the recommended value is between 1k - 4.7k.

VDD I/O can differ from VDD to accommodate the desired interface voltage and can go down to 1.71V. For single-supply operation, VDD I/O can be the same as the main supply, VDD (1.95V to 3.6V).

Regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am able to do I2C writes to the 8652 fine (predictable and expected behavior from the accelerometer). But I am unable to read back registers. SCL & SDA when viewed on scope show OK levels and waveforms. Even a read of the 'who am I' reg returns either 0x00 or 0xFF. This makes me wonder about VDDIO in the datasheet:

- Why the strong pullup (1k resistor) to VDDIO? Paragraph 1.3.

- Table 5 shows typical VDD as 2.5v but typical VDDIO as 1.8v.

- Table 1 has the footnote "The control signals SCL and SDA are not tolerant of voltages higher than VDDIO + 0.3 V. If VDDIO is removed, then the control signals SCL and SDA will clamp any logic signals with their internal ESD protection diodes."

Harold

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Harold,

Could you please post here the waveforms to review what is going on on the I2C bus?

A single byte read e.g. from the WHO_AM_I register 0x0D should look like this:

A common problem with the read operation is sending a stop condition (a low to high transition of SDA while SCL is high) after the second byte (in this case 0x0D). The correct way is to release the SDA line (so that it transitiones to high) before the SCL line goes high.

As for the pull-up resistors, the recommended value is between 1k - 4.7k.

VDD I/O can differ from VDD to accommodate the desired interface voltage and can go down to 1.71V. For single-supply operation, VDD I/O can be the same as the main supply, VDD (1.95V to 3.6V).

Regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK. I verified that the repeat Start condition for a read works, and apparently is mandatory. For all other I2C devices I work with, the repeat Start condition is optional and the register address is remembered.

I now consider this question answered. Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Do you mean that the register address (1st data byte of the write message) does _not_ persist after the Stop condition?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Harold,

It would be useful to see your complete source code or at least accelerometer initialization so that I can reproduce your settings.

It is correct that it is necessary to read the TRANSIENT_SRC register to clear the SRC_TRANS bit in the INT_SOURCE register and consequently deassert the interrupt. You might find helpful the attached example code where I illustrate it on the tap detection function.

I hope it helps.

Regards,

Tomas

PS: If my answer helps to solve your question, please mark it as "Correct" or “Helpful”. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I want to use transient detection to log events (harsh, sharp jolts) that may be harmful to the assembly. So I am interested in all axes and will eventually set the threshold high, 8g; the high pass filter should keep out low frequency events.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is not likely that my board is holding the interrupt (from the accelerometer to the micro) low:

- If I short the interrupt line (pulled high on board, interrupt configured as open drain + active low) to ground, I see the signal pulled low in the micro; and when I subsequently let if float the signal as seen by the micro goes high.

- Even if the board was holding the interrupt line low, that would not explain why I see 0xFF in both the interrupt source and transient source registers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Setting DBCNTM in the TRANS_THS reg and clearing ELE in the TRANS_CFG reg helps: no more continuous interrupts. Still, I always see 0xFF in both the TRANSIENT_SRC and INT_SOURCE regs.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content