- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

how does write data to flash memory in s32k314?

I am trying to develop a bootloader for the NXP S32K314. and s32ds IDE version is 3.6.1, RTD is 4.0.0.

From what I understand, I need to divide the internal flash memory into two separate regions: one for the bootloader and one for the application.

1. If that is correct, how can I determine the bootloader region and the application region, and how do I allocate and separate those areas?I think this can be done through the linker (.ld) file, but I want to know exactly how the flash memory address ranges are organized.

2. how do I program the bootloader code into the bootloader region?

3. how do I perform flash-writing operations on the S32K314?

4. if you have bootloader source code example for writing flash memory, would i get?

i have to develope a bootloader by low-level driver.

1. i included C40_IP. and do i need a Cache_IP driver for writing flash memory?

2. does s32k314 has a cache? so when i write data to flash memory, do i have to control cache memory?

3. what is AB Swap of HSE firmware and OTA? would you explain about that?

Hi @rlaxortn,

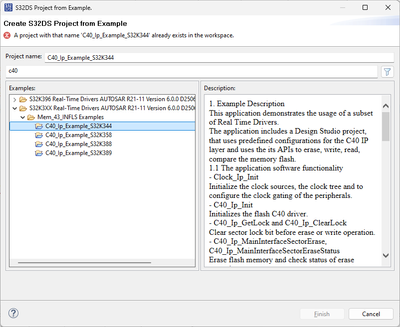

1. & 2. Yes. It's better to manage the cache coherency so the CPU does not read stale data. You can refer to the C40_Ip_Example provided by the RTD package; it shows how to initialize the driver, clear the sectors before E/W, and reads the data.

Also, you can refer to chapter 4.1.55 (Parameter MemSynchronizeCache) from RTD_MEM_43_INFLS_UM.pdf (MCAL layer of C40_Ip driver):

...\S32DS\software\PlatformSDK_S32K3\RTD\Mem_43_INFLS_TS_T40D34M60I0R0\doc\

3. A/B swap is HW assisted, managed by HSE firmware. When OTA is enabled in the part, device flash is divided in 2 blocks.

- Active block, where the application code is located.

- Passive blocks, where the rollback image is located

You can find some information in the previous links I've shared, as well as this presentation: S32K3 OTA AB SWAP DEMOSTRATION.

There is also the Unified bootloader Demo, which is a UDS bootloader solution for S32K3xx, however it is provided as is with no further support.

Best regards,

Julián

Hi @rlaxortn,

1. Yes, this can be done through the linker file, however, I suggest going through the HSE Firmware and OTA presentation under "Documentation -> Secure Files" from S32K3's product page. Silde 82 shows the S32K3XX Memory Architecture, as well as FOTA overview through the A/B swap use case.

2. Please refer to the community post shared below. AB swap is performed by HSE service, so it's necessary to have AB swap version of HSE firmware installed. Solved: Re: s32k3 flash swap requirements? - NXP Community.

3. You can use C40_Ip (low-level driver) flash interface or Mem_Infls (MCAL driver) for flash operations. There is AN13388 which you can use as introduction.

4. You can refer to the S32K3 OTA demo under S32K3 Reference Software package. It can be downloaded by searching "Automotive SW - S32K3 - OTA Demo".

Best regards,

Julián