- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Technical Inquiry Regarding Undefined Last Channel in ADC Instance

Technical Inquiry Regarding Undefined Last Channel in ADC Instance

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Technical Inquiry Regarding Undefined Last Channel in ADC Instance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Technical Support Team,

I am writing to report an anomaly observed during ADC data acquisition debugging on an S32K312 microcontroller using the Adc_TS_T40D34M20I2R0 MCAL package (SW32K3_RTD_4.4_2.0.2_D2211). The issue pertains to the incorrect definition of the Last Channel in the ADC instance, specifically affecting DMA buffer population under specific configurations.

Issue Description

Configuration Context:

- Trigger Mode: Hardware-triggered conversion via Timer (1-second interval).

- Data Transfer: DMA-based data transport without interrupt (DMA interrupt handles data movement).

- Channel Setup: Configured multiple channels, with the last channel indexed as Channel 72 (as per EB28.2 configuration).

Observed Behavior:

- The first channel index in the configuration fails to populate the designated DMA buffer, despite the PCDR register confirming successful data acquisition (register values match expected analog inputs).

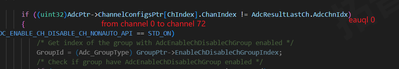

- Debugging reveals that the function Adc_Ipw_CalculateLastChan() — responsible for determining the last converted channel — consistently returns AdcResultLastCh.AdcChnIdx = 0 instead of the expected 72.

- The first channel index in the configuration fails to populate the designated DMA buffer, despite the PCDR register confirming successful data acquisition (register values match expected analog inputs).

Root Cause Analysis:

- In the function Adc_Ipw_CalculateLastChan() (invoked as AdcResultLastCh = Adc_Ipw_CalculateLastChan(Group, ConversionType, CoreId);):

- The initialization of AdcChnIdx defaults to 0 and never updates to reflect the configured last channel (Channel 72).

- In the function Adc_Ipw_CalculateLastChan() (invoked as AdcResultLastCh = Adc_Ipw_CalculateLastChan(Group, ConversionType, CoreId);):

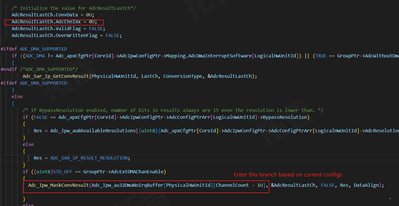

Subsequent logic (e.g., DMA buffer assignment) erroneously treats Channel 0 as the last channel, causing data for Channel 72 to be skipped in the buffer.

4. Code Modification:

Revised Adc_Ipw_CalculateLastChan() to initialize AdcChnIdx with the configured LastCh value (72) instead of 0.

- Post-modification, AdcResultLastCh.AdcChnIdx correctly returns 72.

- DMA buffer now successfully captures data for all channels, including Channel 72.

- Request for GuidanceOpen Questions

Potential Oversight:

- Is there a configuration parameter or runtime condition (e.g., group/conversion mode) that should update AdcChnIdx but was missed in our analysis?

- Does the MCAL design implicitly assume Channel 0 as the last channel in certain modes?

Suspected Bug:

Given that the default initialization (AdcChnIdx = 0) contradicts the configured channel topology, is this a latent bug in the MCAL implementation?

- Could you verify whether this behavior aligns with the intended design of Adc_Ipw_CalculateLastChan()?

- If confirmed as a bug, is there a planned patch for the MCAL package?

- Alternatively, are there workarounds beyond the described fix?

Thank you for your expertise and prompt attention to this matter.

Best reagrds,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've taken the time to check the latest RTD versions, and the following changes have been made in RTD 4.0.0 and later, such as RTD 5.0.X and RTD 6.0.x.

This is likely a known and fixed bug. I recommend that you stop using older versions of RTD.

You may encounter new issues later, but these issues may have been fixed in newer versions,

and we don't have the resources to help you reproduce issues with older versions.