- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

background:

chip s32k341,

SPD 1.0.4 version,

WDG->WDGEOC = 0x61A7UL.

problem description:

ST_DONE functional reset happened after running Bist_Run(BIST_SAFETYBOOT_CFG), reading ERR_STAT register shows that WDTOSW bit and RFSF bit are set.

What are the possible reasons?

thank you.

已解决! 转到解答。

I finally solved the problem, and maybe I can give you some help:

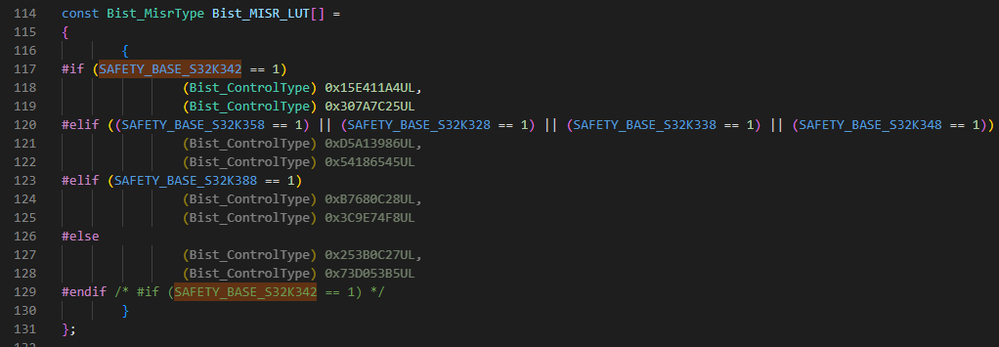

1. I chose s32k341 in EB, but there is a macro definition only s32k342, resulting in an incorrect value.

2. My project does not use QSPI and EMAC, but BIST needs to enable the clock of these peripherals.

Hello,

In other words, your watchdog timer guarding BIST execution has expired and BIST was aborted.

You can enhance timer in the STCU2 Watchdog Granularity (WDG)

RFSF is most probably set due to the WDG timeout.

Best regards,

Peter

Hello,

I try to increase the STCU2 Watchdog Granularity (WDG) to 0x2625A00(about 16 seconds), but the result doesn't change.

The codes also meet these prerequisities:

STCU2 regs after ST_DONE functional reset are shown below.

Could there be other causes?

thank you

Hello,

Hmm, ok. I never used SPD to run the BIST.

But you can also have following issue:

Can you play with pointer and reduce number of concurrent BIST running? Not sure which degree of configuration SPD offers.

Also, it is possible

https://community.nxp.com/t5/S32K/STCU2-internal-errors-and-SPD-BIST-BIST-DIAGNOSTIC-CFG/m-p/1813872

best regards,

Peter

I finally solved the problem, and maybe I can give you some help:

1. I chose s32k341 in EB, but there is a macro definition only s32k342, resulting in an incorrect value.

2. My project does not use QSPI and EMAC, but BIST needs to enable the clock of these peripherals.