- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

S32K314 advanced secure boot, JTAG can't connect

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

1.S32K314, External oscillator:16M, HSE firmware version:s32k344_hse_fw_0.5.0_2.40.0_pb230807.bin.pink

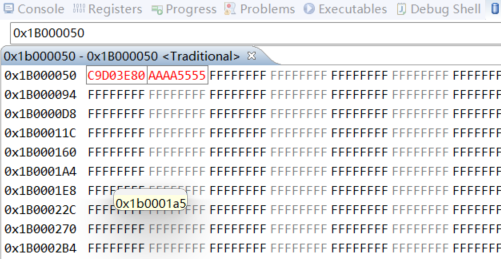

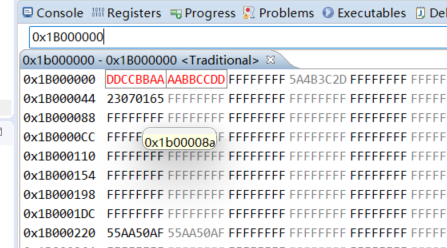

2.configure utest area: 0x1B000000 and 0x1B000050 already has been configured. DcfClockOption don't configure, because S32K314 have a default value ,meet option A(80M), you can see picture.

3.Then I configure advance secure boot(SMR and CR table), based AES128CMAC algorithm.

4.If I set advance secure boot, after reboot, execute secure boot, it's ok. But If I enable PLL(TempIvt.bootCfgWord |= (IVT_BOOT_CFG_WORD_BOOT_SEQ |IVT_BOOT_CFG_WORD_PLL_ENABLE);) when configuring secure boot, after reboot, code can't run rightly, and S32K314 will reset continuously.

5.we has been test in 8M and 16M External oscillator, the result is same. Of course, the user core we has configured to 160M(HSE only can be configured to 80M[option A]).

Notes:when we use old version HSE firmwire(s32k3x4_hse_fw_0.5.0_2.1.0_pb220625.bin.pink),don't have this question.

this pictures is our utest value when use 16M External oscillator.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @JiayuZhou

Could you please share your device's SBAF version (address 0x4039C020) to help rule out any potential issues related to it?

BR, VaneB

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We have been use the latest SBAF version(s32k344_Secure_Baf_0.5.0_0.15.0.6_pb230807.bin.pink)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @JiayuZhou

Could you please assist us by sharing an image that shows the memory values of the IVT (Interrupt Vector Table)? This will help us verify the BCW and ensure that the requirements to configure PLL and FXOSC as the HSE clock source during boot are properly fulfilled.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

thank you for answer. Currently, we have been found the reason. When enable PLL, Because the external 1.5V power supply drive capacity is insufficient, resulting in lower voltage than required, then S32K314 reset. could you confirm that chip will reset when 1.5V lower than required?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @JiayuZhou

According to the Hardware Design Guidelines for the S32K3 Microcontrollers, during the power-on sequence, the power supply must ensure a controlled ramp rate from VDD_OFF (0.1V) to the operating voltage levels of VDD_HV_A, VDD_HV_B, and V15. If the ramp rate is not within the specified range, it may lead to unexpected behavior, system malfunctions, or even permanent damage to the MCU.