- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Currently, I am working on S32K312 SAF EVAL Package. I am using S32K312EVB-Q172, PE Micro debugger and S32DS using RTD Build version S32K3_RTD_3_0_0_P07_D2306_ASR_REL_4_7_REV_0000_20230629.

Target - Debug_FLASH.

I have a query related to STCU2 debugging.

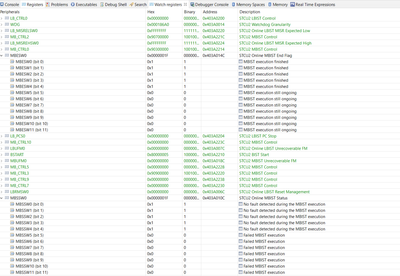

After functional call of Bist_Run(BIST_DIAGNOSTIC_CFG); PE Micro debugger getting disconnected. so, I am not able to see watch register.

I have query on below points.

1. Why PE micro debugger is getting disconnected after call of Bist_Run(BIST_DIAGNOSTIC_CFG).

2. After disconnected the PE debugger, I observed software is reset and again start executing, tested with LED blinking. is it expected behavior?

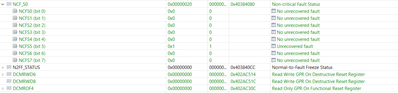

3. Without Power off the hardware, after re-flashing then I check the status of FES register Bit ST_DONE found set. But STCU2 related register value is in default state. is it expected behavior?

4. According to S32K3 RM, FES register bit ST_DONE bit will be set post self-test. so, I am assuming STCU2 test is successfully done. is it expected behavior?

5. After power on reset of hardware FES register value is 0.

6. How can I see the register status of STCU2. Because PE debugger getting disconnected?

Please see the below attached screenshot.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @raj12,

1. Yes, system reset disconnects the debugger.

2. Yes, it boots up again.

3. The FES, DES register show the source of the latest reset. But the peripheral registers are reset. The RM specifies the reset value for each register.

4. Yes

5. After POR, you should see just DES[F_POR] = 1.

6. The PE Micro debugger can be attach to the running MCU after the ST_DONE reset without a reset triggered by the debugger (FES[F_EXR]).

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @raj12,

1. Yes, system reset disconnects the debugger.

2. Yes, it boots up again.

3. The FES, DES register show the source of the latest reset. But the peripheral registers are reset. The RM specifies the reset value for each register.

4. Yes

5. After POR, you should see just DES[F_POR] = 1.

6. The PE Micro debugger can be attach to the running MCU after the ST_DONE reset without a reset triggered by the debugger (FES[F_EXR]).

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @danielmartynek ,

Thanks for your quick reply,

Now my previous query got resolved after your reply.

Now I have another query related to STCU2.

1. I tried to insert fake fault of FCCU which is NCF_5. then while debugging observed ERR_STAT register bit 8 is in high state, FES register bit 4 ST_DONE in high state, NCF_S0 register bit 5 in high state, MBESW0 bit 1 to 5 in high state, MBSSW0 bit 1 to 5 is in high state. So, I am assuming BIST is functionally fine. is it expected behavior for NCF_5? please see the attachment.

2. For other FCCU NCFn (apart of NCF_5) any bit in ERR_STAT register why not in high state? apart of ERR_STAT other register of STCU2 is same as NCF_5 FCCU fault injection?

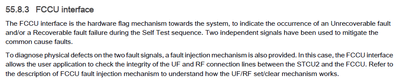

3. What is the co-relationship between NCF_5 (FCCU NCF_5) and STCU2, ERR_STAT register or STCU2? I tried to refer RM but unfortunately not able to be understood (55.8.3). please see the attachement.

4. After injection of FCCU NCF_5 error, called Bist_GetExecStatus(BIST_DIAGNOSTIC_CFG), function then got BIST_FAILED. is it expected behavior for NCF_5? if yes then why?

5. But for other NCFn called Bist_GetExecStatus(BIST_DIAGNOSTIC_CFG), function then got BIST_OK. is it expected behavior for other NCFn (apart of NCF_5).? if yes then why?

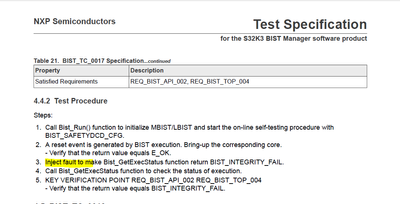

6. Which NCF Fault we should need to inject for STCU2 fault checking? I am trying to run test procedure which is provided in S32K3XX_SAF_BIST_TS.pdf (Page number 14). I am attaching snapshot below kindly look onto that.

I am looking forward for your reply.

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告