- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

S32K1xx LPI2C RX Command Question

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am implementing a driver for the S32K1xx family's LPI2C peripheral and am trying to understand the RX command behavior.

For example, if I load the following set of commands into the TX FIFO:

- CMD: 0x04 DATA: 0x55 (Generate START + Address)

- CMD: 0x01 DATA: 255 (Receive 256 bytes)

- CMD: 0x02 DATA: 0 (Generate STOP)

I then enable the RDF interrupt by setting MIER.RDIE to 1.

I then have an interrupt handler that handles processing the RDF event. If I place a break point in the interrupt handler, based on what I read in the reference manual, I would expect to see four bytes get clocked in and then have the peripheral stall since the RX FIFO is full. But what I am seeing on my scope is the break point hits but all 256 bytes are clocked on the SCL line. This leads me to "missing" all of the bytes due to the breakpoint.

I have MCR.DBGEN set to 1.

Any idea what the expected operation should be?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

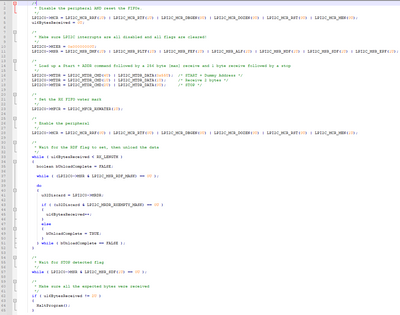

I wrote a little test code to try and understand the behavior of the LPI2C peripheral. It does not use interrupts, but rather polls relevant flags:

If I simply put a break point at line 62 (at the end) this code runs fine and I receive two bytes. But if I place a break point at line 28 where the peripheral is enabled and try and step through the code, I see the whole transfer appear on my scope, and I can step through the while loop that waits for RDF to get set at line 37, but the MRDR register just reads 0x00004000 (RX FIFO empty) and so my received byte counter never gets incremented and I am forever stuck in the while loop waiting for received bytes.

Any idea what is going on? Is the debugger (S32DS) somehow pulling the received bytes out of the RXFIFO before my code can get to them? I would expect when I hit the break point at line 28 and start stepping that at some point I would see RDF get set, see MFSR.RXCOUNT get to 2, and see the first value (without the RXEMPTY flag set) sitting in MRDR. But with stepping, I never see any of that. RDF always appears 0, RXCOUNT always 0, and RXEMPTY always 1.

I have tried this code with MCR.DBGEN both set and cleared. The only difference when it is set is that the entire transfer appears when I do the first step after hitting the breakpoint at line 28, and I never make it past the while at line 37 that waits for the RDF flag to set.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Please close the EmbSys Register view and the Memory view - everything that can read the data register.

Thank you,

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Stephen,

This is the expected operation.

If DBGEN == 1, the LPI2C module continuous operating.

Regards,

Daniel