- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K142: FlexCAN without SOSC

S32K142: FlexCAN without SOSC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

I have a custom board with S32K142 and I did not put an external oscillator on it because it doesn't have space on it. According to this diagram in the reference manual, it is possible to run the FlexCAN module without SOSC:

However, when I disable SOSC and try to initialize CAN, it halts at the can initialization step:

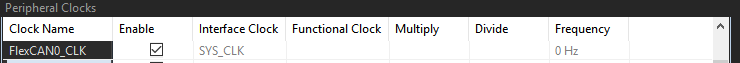

I set the clock source in CAN module to PE clock and it shows that both the module and PE clocks are set to 48 MHz. The clock manager for some reason, shows this:

Is it possible to run CAN without an external clock? If so, How can I fix this?

Thank you,

Harsha

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Apparently this is a known bug in the SDK. The solution was to switch the component to flexCAN and write this in the FLEXCAN_DRV_Init function:

if(((base->MCR & CAN_MCR_MDIS_MASK) >> CAN_MCR_MDIS_SHIFT) == 0U)

{

/* To enter Disable Mode requires FreezMode first */

FLEXCAN_EnterFreezeMode(base);

FLEXCAN_Disable(base);

}

#if FEATURE_CAN_HAS_PE_CLKSRC_SELECT

/* Select a source clock for the FlexCAN engine */

FLEXCAN_SelectClock(base, data->pe_clock);

#endif

The idea is it check first if the module is already in disabled mode as expected to be the peripheral after reset and if is not already disabled then to force the freeze mode and disable the CAN module.

This workaround, at this time, is not possible using the can_pal component.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alexandre,

Do you have enabled the module clock for the instance of the flexcan ?!

Try to read with the debugger the MCR register of the flexcan instance, after the clock initialization and if it crashes that is the problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

Yes, all clocks are set but the debugger cannot read the register.

Furthermore, no frequency are specified into the clock configuration panel in PE.

Indeed, it seems like a clock issue.

After investigation, i found the wrong setting, my system clock is set at 80 MHz.

With a 48MHz clock, registers are accessible.

I don't found a maximum system clock speed in any documentation. Someone have found something about that ?

Thank,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have used the sys_clock set to 80Mhz for PE engine too and the flexcan worked as supposed. The PLL it uses as clock source SOSC how did you generate the SYS clock of 80Mhz ?!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I tried with 8MHz and 80Mhz engine clock, it's same.

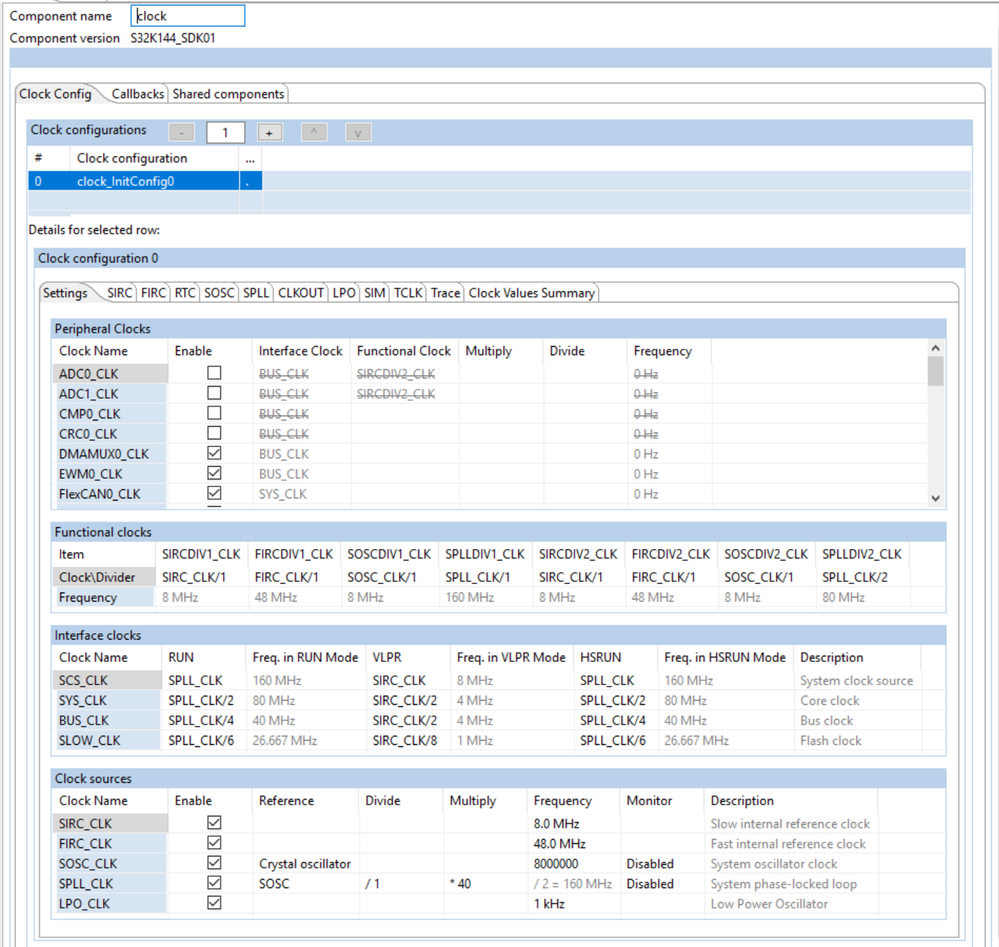

Link below my clock tree.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

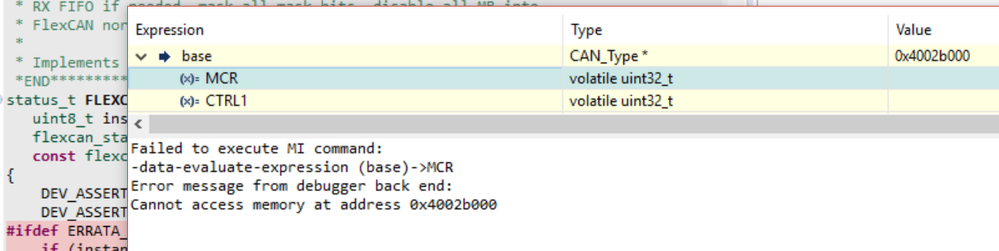

I have the same issue. When the driver try to access of MCR register, the code crash.

I tried the fix above but without effet, the code crash when base->MCR is tested.

Someone have an idea why i can't access to CAN registers. The differences with the sample code is that i work with a 80MHz clock source. (But 8MHz Engine clock).

I also use the no-FD CAN.

Thank,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It's hard to know why. In my case, that fix is working perfectly. Are you using the can_pal component or the flexcan component?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, i use the can_pal.

But it seems like a clock issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Our issues aren't really the same, then. In my case, I used the 48 MHz clock for both system and PE and the SDK wouldn't work well with that until I used the workaround.

I'm unsure why it wouldn't work with the 80 MHz clock. Can you post a screenshot of the debug view when the code crashes?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Of course,

Call stack,

And registers,

Thanks a lot for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

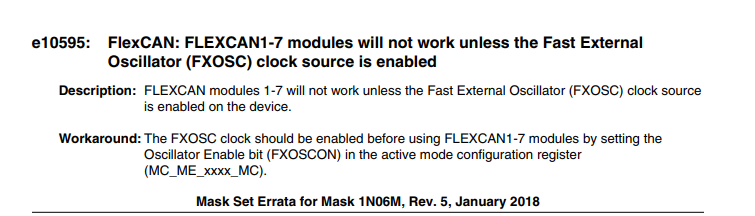

I looked up the errata code and found this:

This document is intended for MPC574XX controller and I don't think that that register exists in S32K1XX. So I don't think ERRATA_E10595 should actually be defined. I would try deleting those lines of code and see if it works.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Apparently this is a known bug in the SDK. The solution was to switch the component to flexCAN and write this in the FLEXCAN_DRV_Init function:

if(((base->MCR & CAN_MCR_MDIS_MASK) >> CAN_MCR_MDIS_SHIFT) == 0U)

{

/* To enter Disable Mode requires FreezMode first */

FLEXCAN_EnterFreezeMode(base);

FLEXCAN_Disable(base);

}

#if FEATURE_CAN_HAS_PE_CLKSRC_SELECT

/* Select a source clock for the FlexCAN engine */

FLEXCAN_SelectClock(base, data->pe_clock);

#endif

The idea is it check first if the module is already in disabled mode as expected to be the peripheral after reset and if is not already disabled then to force the freeze mode and disable the CAN module.

This workaround, at this time, is not possible using the can_pal component.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This workaround apply to can_pal too because it uses the FLEXCAN_DRV_Init function too to initialize the can peripheral.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I tried that and it didn't seem to work. NXP said "The can_pal is a component wrapper over the FlexCAN driver, so don’t have access directly to the Peripheral Registers."

I didn't try to troubleshoot it further because it was just easier to change my component.