- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

S32K118 Clock Monitoring Unit Configuration

Hello,

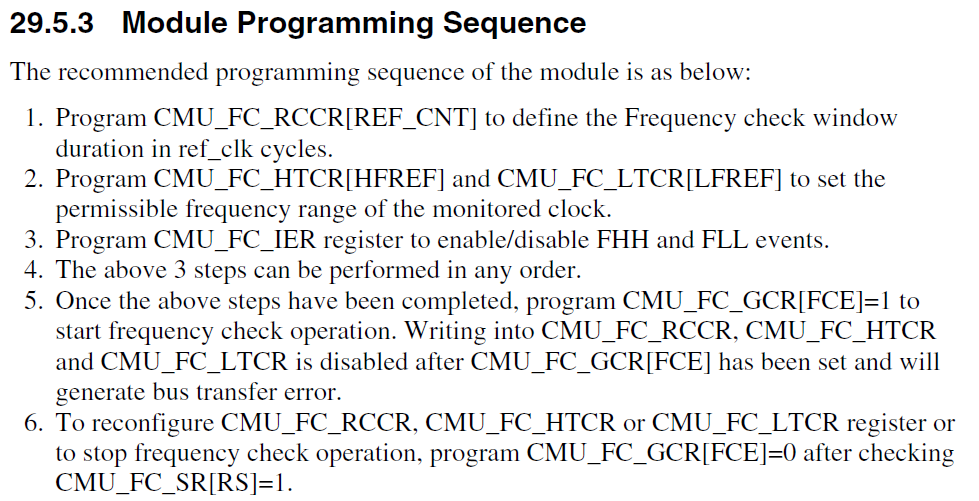

I am working with S32K118 and I am trying to configure the clock monitoring unit according to the below steps in the manual:

However, when trying to write in any register of the clock monitoring unit such as RCCR / HTCR / LTCR / IER / GCR ,

A hard fault exception is generated and I am unable to change the registers' value at all.

Is there some protection on these registers that I have to unlock before writing?

Appreciate your kind help.

Thanks and Regards.

Hello Daniel,

Thank you so much for your answer. This was indeed the issue.

However I have another inquiry about the clock monitoring unit, I understand I can manipulate the thresholds in HTCR and LTCR registers to generate a Loss of Clock reset when monitoring the FIRC, I already tested that. But how can I change the CMU configuration to generate the same reset using the internal SOSC (8MHz) in S32K118 EVB? or does the CMU monitor only the FIRC?

Thanks and Regards,

Sherif

Hello Sherif,

CMU does not monitor SOSC.

Section 25.2.2.4 Loss-of-clock (LOC), RM rev.9. shows how to enable the SOSC monitor.

Regards,

Daniel