- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K116EVB DMA SPI Slave Data misalignment

S32K116EVB DMA SPI Slave Data misalignment

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K116EVB DMA SPI Slave Data misalignment

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I encountered a problem while debugging the S32K116EVB-Q048 evaluation board.

- phenomenon:

I use S32K116 as a slave in SPI communication for debugging. The host is only responsible for sending a frame of 8 bytes of instructions with a period of 1ms. After receiving the instructions from the host, the S32K116 slave returns the corresponding data.

Configure the DMA1 module in S32K116 to receive and store SPI, and configure the DMA2 module to send data to the host for SPI.

After the host sends 8 bytes of instructions, the SPI slave of S32K116 uses DMA1 to store the data in the corresponding Rx_Buffer array after receiving the data, and at the same time uses DMA2 to fill the data in Tx_Buffer into the TX FIFO register of SPI. This is the process of completing one communication between the master and the slave.

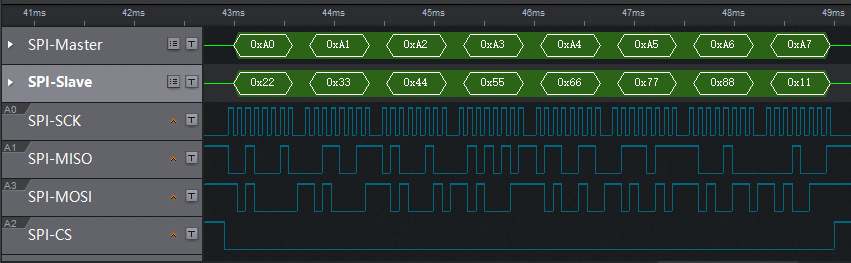

The content of the command sent by the master is {0xA0,0xA1,0xA2,0xA3,0xA4,0xA5,0xA6,0xA7}, and the content of the data returned by the slave is {0x11,0x22,0x33,0x44,0x55,0x66,0x77,0x88}.

- Problem: After the host sends the command, the data content of the received slave is misaligned. The content actually received by the host is: {0x77,0x88,0x11,0x22,0x33,0x44,0x55,0x66}.

Has anyone encountered a similar problem, please help answer it, thank you.

Attach the code. IDE:S32DS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you scope the bus and show the results?

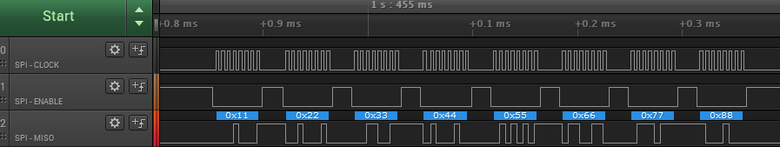

I tested the code you attached unmodified and this is what is I see on the bus:

Thanks,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

BR, Daniel

Thank you for helping me solve the current problem

I changed a chip as the host, and now the SPI host can receive the data in the correct order {0x11,0x22,0x33,0x44,0x55,0x66,0x77}.

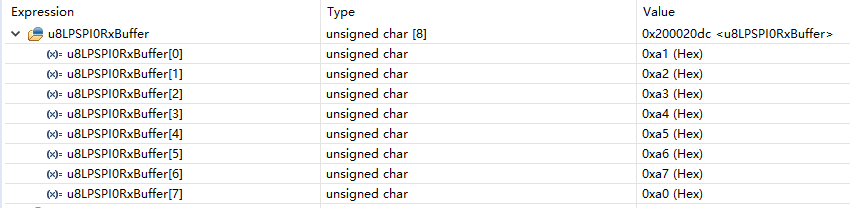

But now there is a new problem. The information received by the SPI slave from the master is also misplaced. The SPI master sends {0xA0,0xA1,0xA2,0xA3,0xA4,0xA5,0xA6,0xA7}, but the SPI slave The received data becomes {0xA1,0xA2,0xA3,0xA4,0xA5,0xA6,0xA7,0xA0}. As shown below.

There is another phenomenon: if I disable DMA2 and only let the DMA1 module in the SPI slave be responsible for receiving the data from the SPI master, then the data received by the SPI slave becomes the correct data {0xA0,0xA1,0xA2,0xA3, 0xA4,0xA5,0xA6,0xA7).

I don't know if you can reproduce this problem, and can you help me answer this question, thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

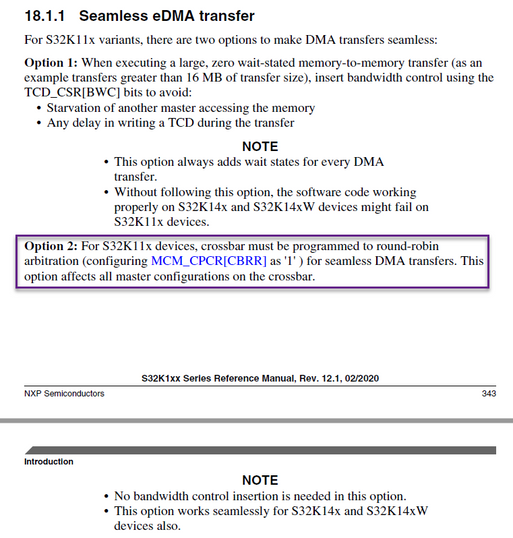

Please try using Round robin arbitration on the crossbar switch (MCM_CPCR) and for the DMA channel selection (CR_ERCA).

Thank you,

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

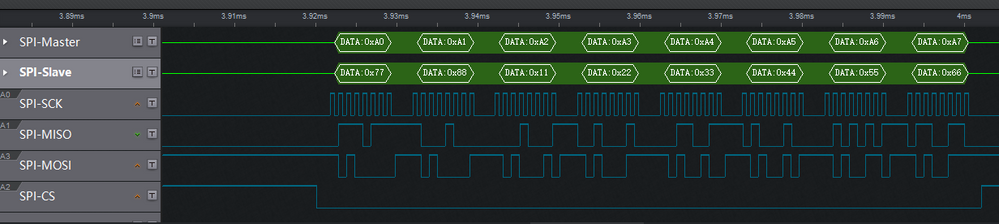

1.The SPI bus frequency of the host I use is 4MHz~6MHz, and then the data will be misaligned.

What is the SPI bus frequency set by your host?

If the SPI transmission bus frequency is to use 4MHz~6MHz, is it impossible to avoid this misalignment problem?

2.I set the SPI bus frequency of my host to 11KHz, and the data obtained is as follows.

Does this mean that there is a problem with the host? Or is it caused by the hardware connection between the host and the slave.