- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Hi,

i same problem here, in chapter 44.3.1 (ref. manual 8, 06/2018) i would like to know the PDB trigger sources. it says

"Refer to chip configuration details for the actual PDB input trigger"

but i cant find it. in the attached excel files are only the trigmux trigger which dont fit into 4 bit.

thanks!

已解决! 转到解答。

Hello Felix,

In section 44.1.1.2 of the reference manual says: "On this device, the PDB trigger source selection is implemented through the TRGMUX module. For each PDB unit, there is only one trigger input from TRGMUX, but it supports different trigger sources. The internal trigger mux inside PDB is not used anymore."

So, from the Trigger input source select, the only option you have is 0000 Trigger-In 0 selected. All the other options are now reserved.

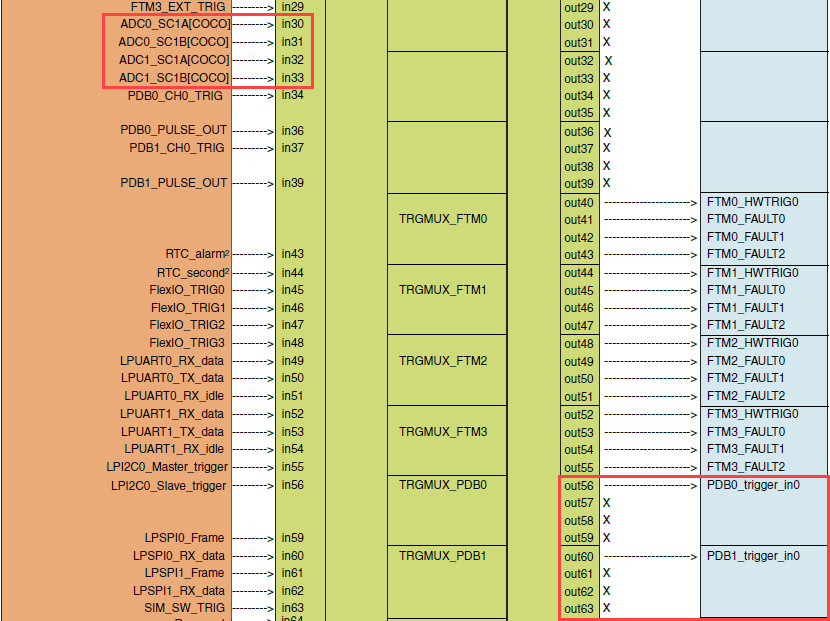

From the RM Figure 19-2, you can see that you have the following Trigger Source options: ADC0_SC1A[COCO] in30, ADC0_SC1B[COCO] in31, ADC1_SC1A[COCO]in32, and ADC1_SC1B[COCO] in33. For example, If you want to target module PDB0_trigger_in0 with ADC0_SC1A[COCO] then in the field SEL0 of the register TRGMUX PDB0 you need to put the 30.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

To explain it a bit more, i would like to have the ADC sample one channel continuous until i stop it. the samples should be stored by DMA.

The DMA part is working, but i need to have the ADC COCO triggering back the PDB so it starts the next conversion.

for now i can sample the four SC1 inputs but then i need to restart the PDB manual (DMA interrupt or Loop).

thanks!

Hello Felix,

In section 44.1.1.2 of the reference manual says: "On this device, the PDB trigger source selection is implemented through the TRGMUX module. For each PDB unit, there is only one trigger input from TRGMUX, but it supports different trigger sources. The internal trigger mux inside PDB is not used anymore."

So, from the Trigger input source select, the only option you have is 0000 Trigger-In 0 selected. All the other options are now reserved.

From the RM Figure 19-2, you can see that you have the following Trigger Source options: ADC0_SC1A[COCO] in30, ADC0_SC1B[COCO] in31, ADC1_SC1A[COCO]in32, and ADC1_SC1B[COCO] in33. For example, If you want to target module PDB0_trigger_in0 with ADC0_SC1A[COCO] then in the field SEL0 of the register TRGMUX PDB0 you need to put the 30.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi, yes this answers my question. Thanks! Will try it tomorrow.

Am i right that there is no direct way to have the adc trigger it self? Like a continous conversion of one channel?

Regards

Felix

Hello Felix,

You are right. For ADC trigger source options you only have the following signals ADC0_SC1A[COCO], ADC0_SC1B[COCO], ADC1_SC1A[COCO], and ADC1_SC1B[COCO].

Best regards,

Victor.