Problems with the S32K144 FlexCAN message buffer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

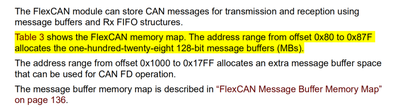

I am programming the S32K144 FlexCAN, About whether this RAMn is a message cache buff?For example,I will reading the data,do I read it from the RAM section 0x80 to 0x87F?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

yes, from address offset 0x80 a message buffer (MB) space is allocated. To send and receive messages you need to set/read those MBs. See chapters 55.5.3-55.5.5 of the device Reference Manual to know the MB structure and a MBs address offset for different RAM block configuration (payload).

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi PetrS,

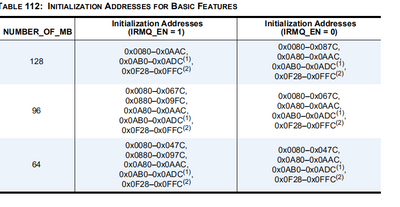

Thank you for your answer.I have another question,What determines the size of FlexCAN RAM message buffer,such as the 16, 32, 64, and 128 parameters.As shown blow:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

what is the document you are referring to?

Each individual MB is formed by 16, 24, 40, or 72 bytes, depending on the quantity of data bytes allocated for the message payload: 8, 16, 32, or 64 data bytes, respectively.

FlexCAN module of the S32K144 has 32MBs max.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi PetrS,

Thank you for your answer. I'm looking at the flexcan ug document.I read your reply, which means that the maximum MB parameter limit is determined by the chip design.