- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi.

I am having the following issue with the UART driver from the S32DS platform:

I'm working on an application in which my S32K116 is the master in an UART communication with an LMM (TPS92662A, for your reference). To write messages, I just follow the LMM-specific UART commands and can succesfully control it. On the other hand, when asking the LMM which is its current status (SC,OC, OT...), I need to send a message through UART and right away listen to the LMM response which carries its status.

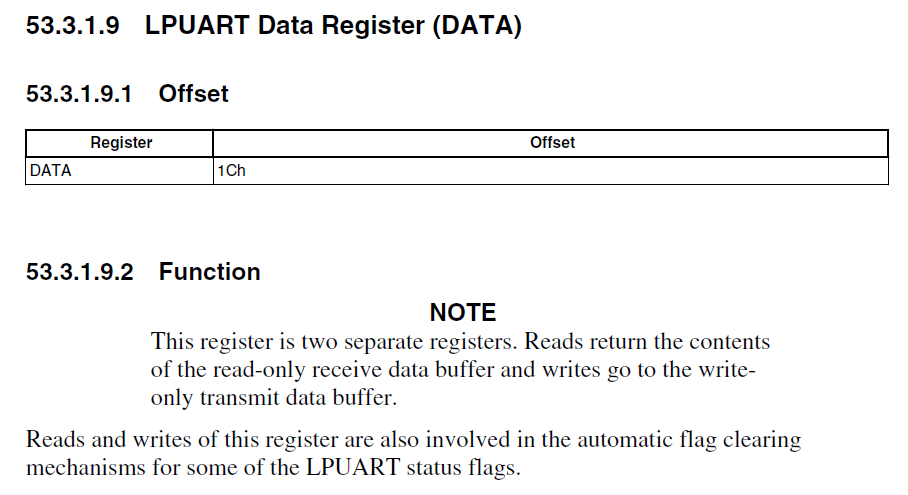

When I send or receive a UART message, the same IRQ is triggered. This IRQ checks for receive data full interrupt or transmit buffer empty. Both cases are checked and they both access to the LPUART register called DATA.

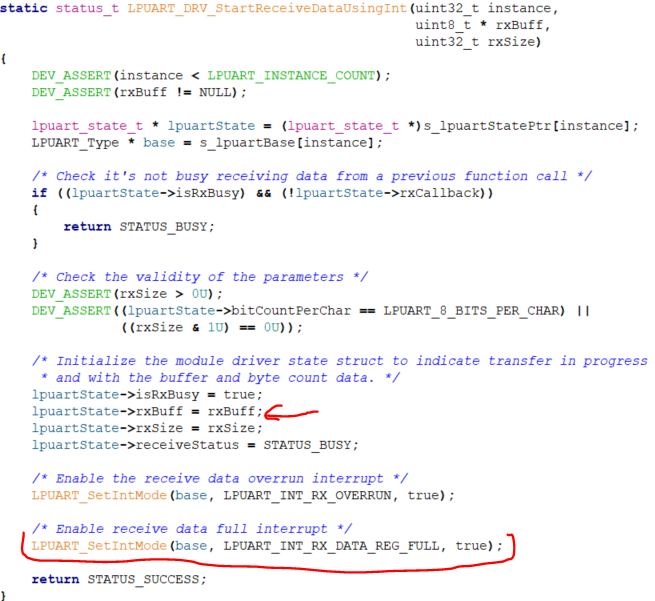

When I call the function to receive data, that function does two things: sets the buffer I send to it as the receive buffer and enables the receive data full interrupt. If this interrupt is not activated, we will not receive any message. See image below:

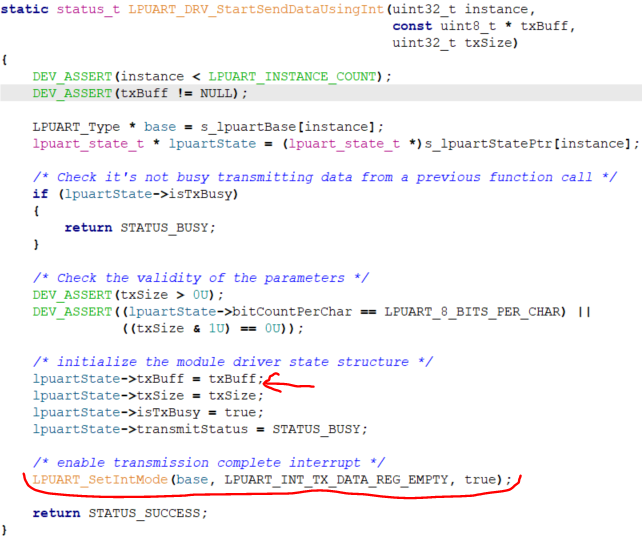

On the image, arrow points to the part where my buffer is set as the receive buffer and underlined instruction is where the interrupt receive data full is enabled. Same process is applied to the send message function.

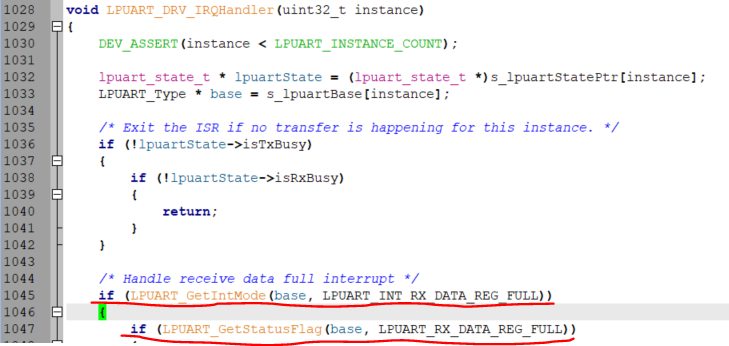

If the receive OR the send interrupt is triggered, both go to the same IRQ. This IRQ does the following:

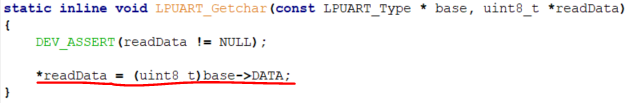

- If the receive data full interrupt is enabled, we get the value from the sub-register DATA of the register LPUART and put it into our receive buffer.

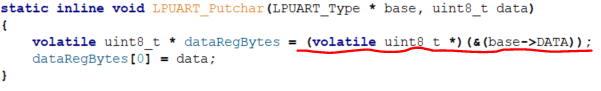

- If the send data empty interrupt is enabled, we put the values from the send buffer to the sub-register DATA of the LPUART register.

Since these cases are not exclusive, if we need communication where we are the masters and our slave responds to our commands, there is a high chance of us getting the values that we are sending into our receive buffer, since we need to listen to the information our slave is going to send to us right after we send our message.

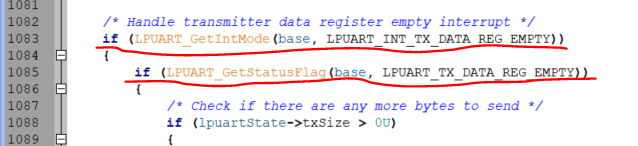

I divided the above function into two screenshots to avoid having a font size too small to read. These if-statements are both in the same IRQ. And we are having the problem I just described:

The data we are sending is being picked up by our receive buffer, making it nearly impossible to know where is the data I need from my slave. As I said before, both access the same DATA sub-register of the LPUART register.

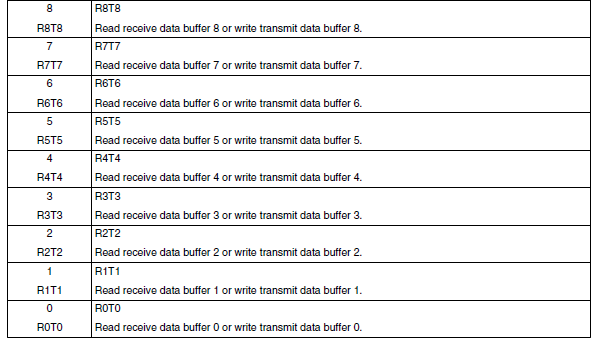

The screenshot above was directly taken from the S32K reference manual.

As it can be seen on the images above, RX and TX access the same register. So, my question is:

Am I missing something to avoid this from happening? Is there a way to avoid/stop the receive buffer from picking up data that is being sent and not received?

Thank you beforehand for your assistance and sorry for the long post.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jose,

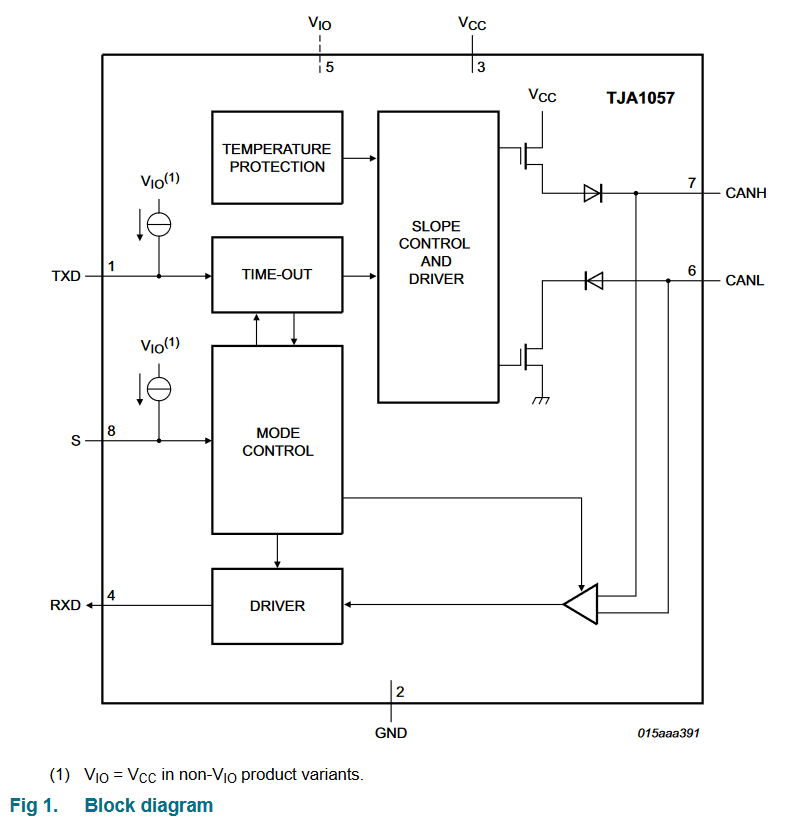

The TJA1057GTK CAN transceiver simply translates the CAN_H/L signal (including everything the TJA1057 is transmitting) to RXD - this can't be disabled.

Could you elaborate on the last sentence?

Do you mean the LPUART RX FIFO reads different data than the logic analyzer shows?

Or the does the logic analyzer show wrong RXD signal? If so, please measure the differential CANH/L signal as well.

Thanks,

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jose,

The LPUART_DATA register consists of two registers.

The RX register is a read-only register and the TX register is a write-only register.

A read from this DATA register cannot return the TX data but always the RX data.

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Daniel, thanks for your response.

I also got to read that part of the reference manual, but I didn't quite understand what made the difference between the RX and the TX buffer, since software seems to be accessing the same address for both, LPUART0 base address -> DATA.

How does the software make a difference between both buffers, since it is accessing the same address for TX and RX and our software is showing TX data in our RX buffer?

Thanks and regards

Jose.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Jose,

Do you monitor the bus with a logic analyzer?

Is there a difference between the RX signal on the bus and the RX data from the DATA register?

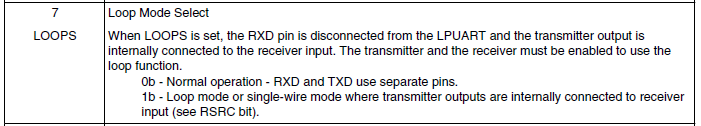

The DATA register cannot return TX data, unless there is a HW issue or the LPUART module is in this LOOP mode:

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Daniel, thank you for your response.

I checked with a logic analyzer the status of my communication, and I got the following result:

My setup uses the CAN transceiver TJA1057GTK, which I believe is also from NXP.

As you can see on the screenshot, TX pin shows TX data and RX pin shows TX+RX data. Is there a way to configure the UART driver or the CAN Transceiver (in case it is indeed from NXP and you know how to do it) so that my reception ignores TX data?

It could be easily filtered if it was behaving as good as the screenshot shows. My software is getting mixed data, sometimes it shows the communication frames as good as the logic analyzer did and some other times I get weird data mixes.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jose,

The TJA1057GTK CAN transceiver simply translates the CAN_H/L signal (including everything the TJA1057 is transmitting) to RXD - this can't be disabled.

Could you elaborate on the last sentence?

Do you mean the LPUART RX FIFO reads different data than the logic analyzer shows?

Or the does the logic analyzer show wrong RXD signal? If so, please measure the differential CANH/L signal as well.

Thanks,

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Daniel, thank you for your response.

What I wanted to say is: My application is, as you see, physically receiving TX+RX, which could be easily filtered if we were reading those values as the logic analyzer shows, but that's not the case. My RX is the one that is not reading correctly.

After some testing, we found out that our RX buffer wasn't behaving as it should (reading the exact same values that reach physically the RX pin, shown in the logic analyzer screenshot) because of our baud rate. We are working on an application in which we need to have a baud rate of 500 Kbps, which gives a byte time of 16us.

Since the UART driver works triggering an interruption each time we receive a byte, it is being triggered way too fast and frequent when we receive an UART message. That's why I wanted to disable this transceiver echo.

I want to try using the FIFO, but it might also get overrun since it can only hold 4 data words.

To use the FIFO, do I only change the FIFO and the RXWATER and that's it? Same receive process?

Another thing that might be even better is to use the DMA, which can be faster and hold as many bytes as we want it to receive, right? Is this correct?

Thanks again for your help.

Regards, Jose.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Jose,

Please read the error flags in the LPUART_STAT register (OR, NF, FE, PF).

If there is no error reported, the data must be correct.

Regarding FIFO/DMA, I don't think there is a simple answer.

If RXWATER is high, the FIFO can overflow anyway.

But with DMA, I would use RXWATER = 0 and transfer it by single bytes.

BR, Daniel