- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- JTAG Design

JTAG Design

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

JTAG Design

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Goodmorning , i'm in hardware debug phase for my new board.

I can't connect my board to the jtag programmer.

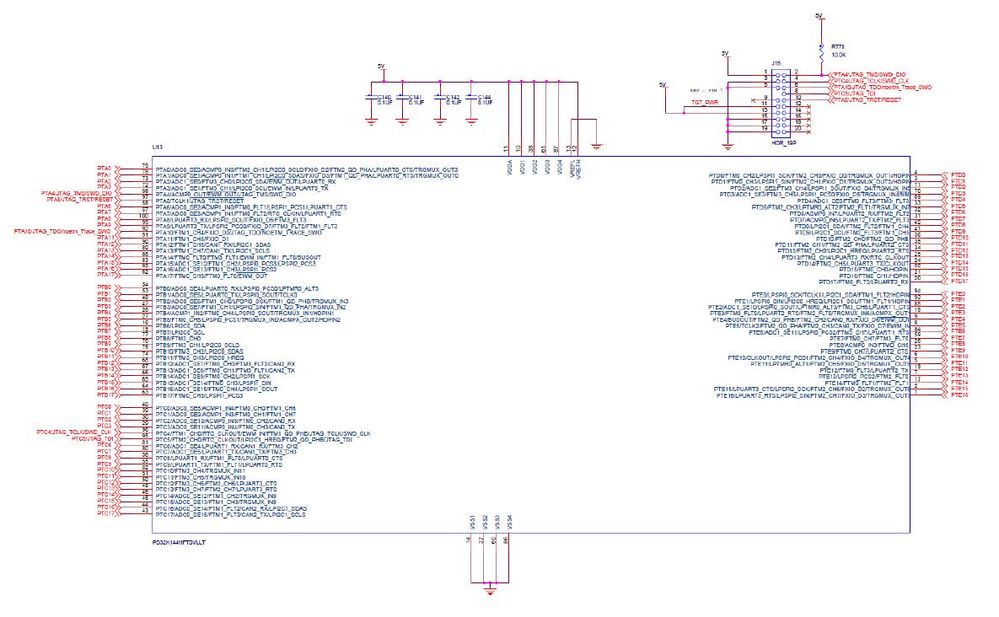

The hardware configuration is very simple, i just followed the Hardware design guideline as shown in the following picture:

The used microcontroller is the S32k144

Can someone help me, please?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

have you tried to check the state of reset pin by oscilloscope? Is the reset deasserted after power on?

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry for my new comment, i'm lookingfor explain this behaviour.

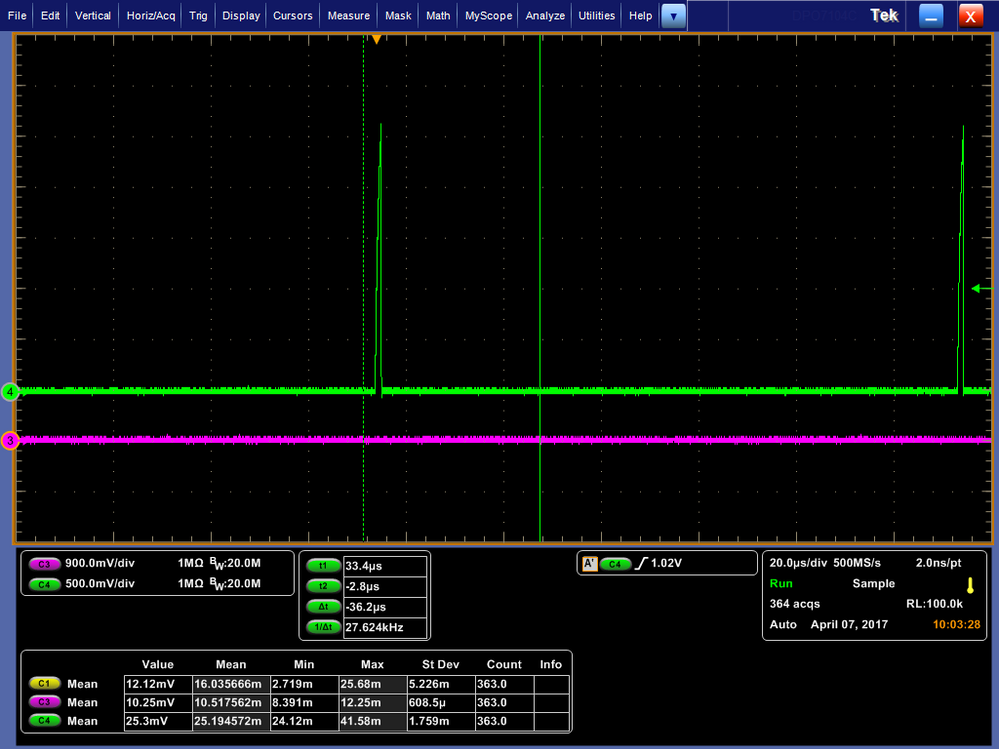

Even on nxp EVB and my custom board, if i full erase chip, i see a kind of spikes signal out from RESET pin as you can see in following picture:

From this state if i force to 3,3V the RESET pin, after i can connect the board to Jlink device and i can use it.

After, if i switch off the board, everything seems to work. But if i full erase the chip, i will force again the RESET pin to reuse the board.

It seems that there are a wrong Handling of the reset pin on first programmation.

All these matters was absent on previuos S32K144 micros.

Can you explain how i can use the reset pin for first programmation?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Pietro,

sorry for delay, I'm very busy now.

I can see there were some changes between cut1 and cut2. There was boot ROM on cut1. After reset, some code has been executed from address 0x1C0001CC. Even if the flash was completely erased, this code was executed and no reset was triggered. This functionality has been removed on cut2 and the program counter is loaded directly with the reset vector from address 0x04. So, if the flash is erased, program counter is loaded with value 0xFFFF_FFFE. Once the execution is started, bus error is triggered. I can see that the device is periodically reset each about 120us (I can see the same waveform as on your screenshot).

So, it's seems to be related to your debugger. It works as expected if I use Lauterbach debugger and also if I use OpenSDA on S32K EVB together with S32 Design Studio - I'm able to establish the communication even if the flash is erased.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, the Reset_b pin is keep at 3,3V after the power on.

Using a Jlink tool i can connect my custom board via SWD.

But i can't connect via JTAG. Is there a particular software configuration to follow?