- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

INTM not working as expected

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have a very confusing problem here.

My chip model is S32K312.

The clock configuration selected is option B. The STM clock is 48M, and the INTM clock is 60M

When the STM timing interrupt is 100ms, my test is as follows:

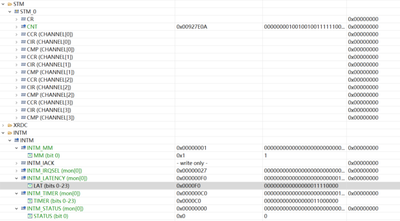

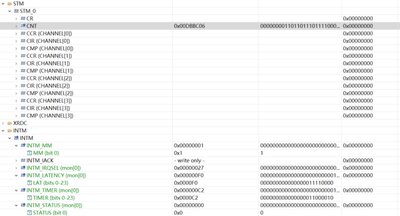

(0x00DBBC06 - 0x00927E0A)/ 48000 = 99.99 According to the value of STM.CNT, we can know that the STM interrupt is triggered as expected, but INTM_STATUS is still 0.

The value of INTM_LATENCY needs to be further reduced before INTM_STATUS changes to 1.

This is also the case when the STM timer interrupt interval is 300ms

I think already I have been very careful to use the INTM interface, but I still don't know where the problem lies

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

INTM allows you to set a maximum timer count for the interrupt latency from interrupt request to interrupt acknowledge. This mechanism monitors the latency of interrupt sources to ensure that these critical interrupts execute within the expected time frame, increasing the reliability of the chip.

Try adding a delay before INTM_IACK instead of increasing the timer period.

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "ACCEPT AS SOLUTION" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I saw your private message, but I can't reply there.

here is my answer

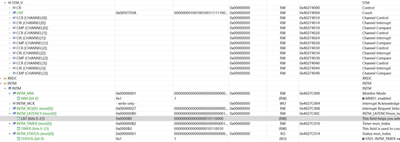

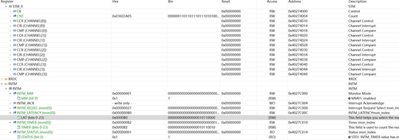

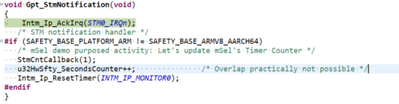

这个帖子我早就看过了,INTM这个模块并不复杂,只有几个寄存器,功能也比较简单,容易理解,但最后就是出现了令人费解的问题,你提到的这个可能性是不存在的,我提问的截图里有STM_CNT的数值,我的断点就是打在了callback中的Intm_Ip_AckIrq函数上,证明两次运行到Intm_Ip_AckIrq的间隔是符合预期的。我也怀疑过难不成STM坏了,改去监控PIT的中断,用STM_CNT作辅助验证,最后还是一样,PIT中断是预期触发,监控结果却总是出错,我注意到一个很奇怪的现象,观察寄存器,STATUS要想为1,TIMER必须大于LATENCY的值,理论上,中断的周期是固定的情况下TIMER的数值每次应该相差不大,但我发现,在监控PIT的时候TIMER的数值会随LATENCY变化而不是中断周期,在监控STM的时候,STM周期变化很大,TIMER的值却几乎不变

附截图

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please add code in the callback to express the value of INTM_STATUS through GPIO output. Timers sometimes behave strangely in debug mode (usually timers have a register to set the behavior in debug mode). If it still doesn't meet expectations, please send me the test project.