- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

How to configure SIRC DIV2 clock in LPTMR component before entering into VLPR/VLPS mode

Hi,

I am working on a project in which during RUN mode I have configured SIRC DIV2 clock with interrupt enable and it is working fine.

For checking the interrupts, I have configured the GPIO. Before controller goes to sleep it will be high and after wakeup it is made as low.

Similarly, I tried to configure SIRC DIV2(8MHz) clock with interrupt enable before entering VLPR/VLPS mode.

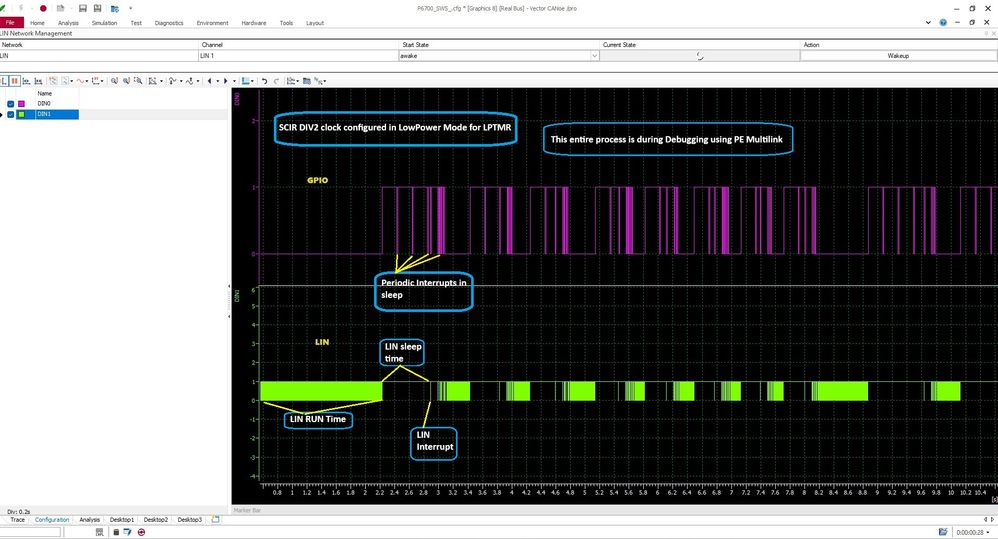

While debugging using multi-link, I am able to get interrupts during sleep periodically as configured. Below is the attached image.

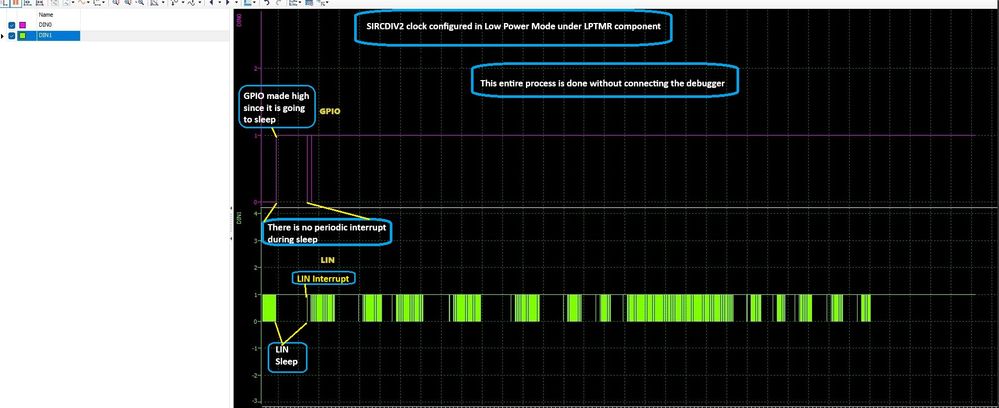

Whereas when I removed the debugger after flashing the code and when I do Hard reset, during sleep I am unable to get interrupts periodically. Before entering it is becoming high and only after giving external interrupt (LIN) it is made as low. It means there is no interrupt happened in sleep. Below is the attached image.

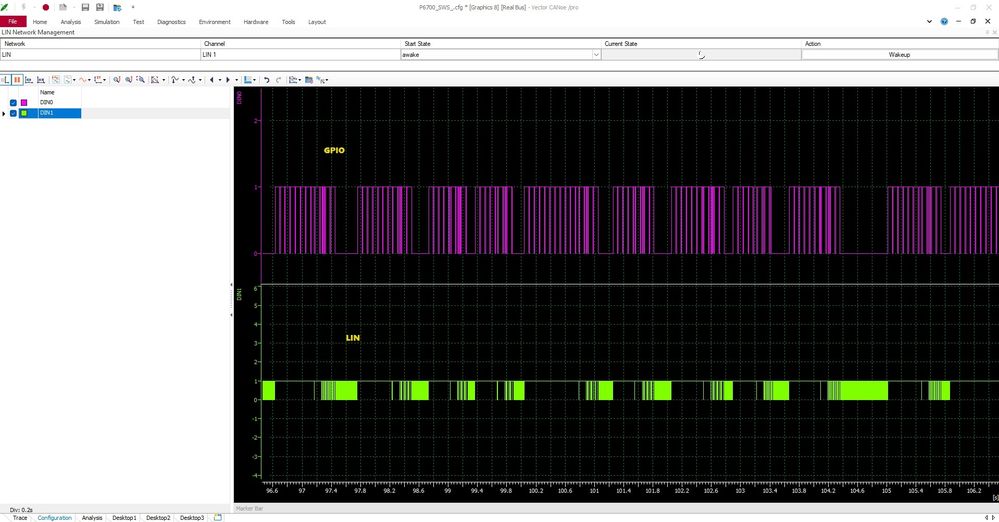

If I configured LPO(1KHz) clock before entering VLPR/VLPS mode. I am able to observe the interrupts periodically. Below is the attached image.

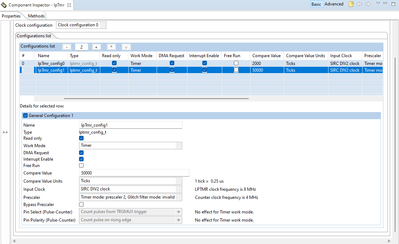

Below are the screenshots of LPTMR configuration with LPO clock and with SIRCDIV2 clock.

With LPO clock:

With SIRC DIV2 clock:

I have attached image below related to code implemented before controller goes to sleep.

In the above image, yellow highlighted indicates that configuring the new LPTMR configuration before entering VLPR. This is where I configured SIRC DIV2 clock instead of LPO clock.

Red highlighted indicates, RUN mode LPTMR configuration is de-initialized.

Blue highlighted indicates, entering VLPR mode.

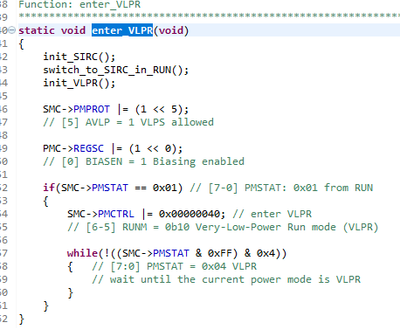

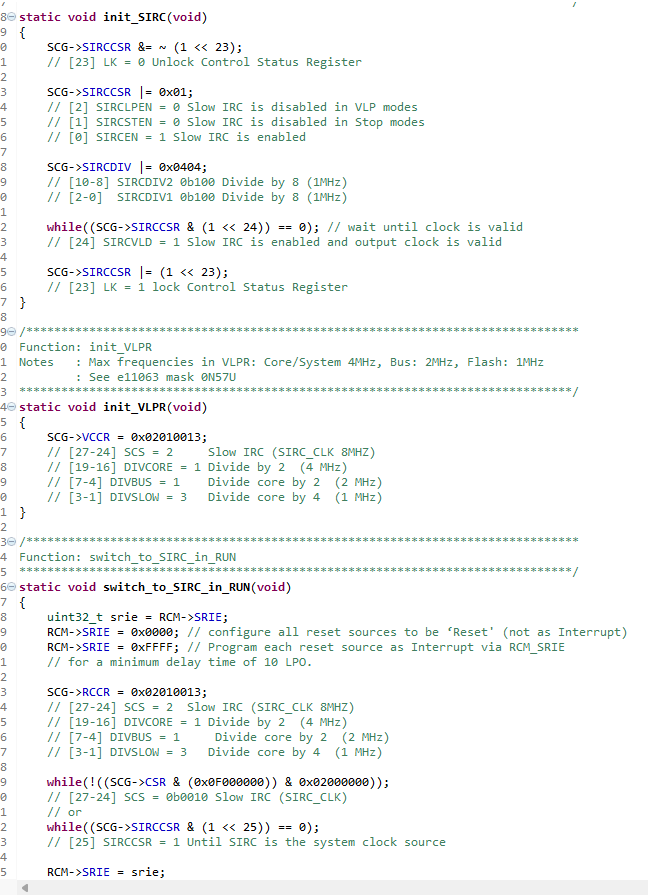

Below is the attached images of VLPR code.

Could you please check the configuration and suggest me if any changes are required either in code or in the LPTMR configuration.

Controller name: FS32K116LFT0VLFT

Ide: S32DS

Compiler: IAR

Hi @Ramsai,

I have noticed that SIRC clock in VLPS is disabled in init_SIRC()

Can you double check the register?

Also, the LPTMR must not be clocked at freq. higher than BUS_CLK

RM, rev.14, Table 27-8. Peripheral clock summary

Regards,

Daniel

Hi @danielmartynek ,

Thanks for the quick reply.

Has you suggested, I updated the changes related to SIRCCSR and also in VLPS mode bus clock is 4MHz and so at LPTMR component level I selected Prescalar has prescalar4_Glitch filter mode 2 clocks (I modified this change because you mentioned that SIRCDIV2 clock frequency should be less than Bus clock frequency.

Attached below is the image of Bus-clock frequency in VLPS mode.

After flashing the code, observed that at LPTMR component level pre-scalar change, my device is not responding after LIN wakeup.

Whereas if I select pre-scalar value to 2, glitch filter mode: invalid then device is responding after LIN wakeup.

Attached the image below and highlighted the related to code changes.

Below image shows the Trace and Graphic view.

Please check the changes and let me know if I did anything wrong or any modification is required.

Regards,

Ramsai

Hi @danielmartynek ,

I already tried by modifying the Pre-scalar value of SIRC DIV2 clock.

1. I generated the configuration with pre-scalar value as "Timer mode: prescalar 2, Glitch filter mode: invalid". You can observe that Counter clock frequency is 4MHz.

Observations: The controller is not waking up periodically. But once LIN wakeup is given the controller is getting wokeup and data is transmitting.

2. I generated the configuration with pre-scalar value as "Timer mode: prescalar 4, Glitch filter mode: invalid". You can observe that Counter clock frequency is 2MHz.

Observations: The controller is not waking up periodically. But once LIN wakeup is given the controller is not getting wokeup and not transmitting data.

In your last reply you mentioned that SIRC DIV2 clock frequency should be less than or equal to 4MHz. So, in above two conditions you can see that the counter clock frequency is less than or equal to 4MHz.

Regards,

Ramsai.

If SIRCDIV2_CLK freq. is higher than 4MHz, the application is out of specification.

We can't guarantee the functionality of the MCU in this case.

Can you first change the source clock freq. and then reconfigure the LPTMR as needed?

Thank you