- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

Flash program on S32K142

Hi,

I met a problem when I program flash. There is line containing 4 bytes to be programmed in the *.srec file. But the driver only supports 8 bytes write. Could I modify the following micro to 4 in file S32K142_features.h?

/* @brief P-Flash Erase sector command address alignment. */

#define FEATURE_FLS_PF_SECTOR_CMD_ADDRESS_ALIGMENT (8u)

/* @brief P-Flash Program check command address alignment. */

#define FEATURE_FLS_PF_CHECK_CMD_ADDRESS_ALIGMENT (8u)

Actually, I've tried to modify, but the function FLASH_DRV_Program() return error, because the FTFx_FSTAT equals to 160, and at the last of the function FLASH_DRV_CommandSequence() will check it. So I think the above two micro could not be modified easily.

/* Check if an error is occurred */

if ((FTFx_FSTAT & (FTFx_FSTAT_MGSTAT0_MASK | FTFx_FSTAT_FPVIOL_MASK | FTFx_FSTAT_ACCERR_MASK | FTFx_FSTAT_RDCOLERR_MASK)) != 0U)

{

ret = STATUS_ERROR;

}

Waiting for your reply!

Best regards,

Sarah

Hello Sarah,

If we check the MCU commands we can find the Program Phrase command which programs eight previously-erased bytes (the smallest portion that can be programmed). So, not driver, but MCU supports 8 bytes write.

The easiest solution for you is to modify and align .srec to 8 bytes.

For this purpose you can use srec_cat tool:

SRecord - Browse /srecord-win32 at SourceForge.net

Examples, how to use it:

https://community.nxp.com/message/937320?commentID=937320#comment-937320

I hope it helps.

Best regards,

Diana

Hi Diana,

Thank you very much. I use the srec_cat tool modify the .srec file. The last line of converted file is 12Bytes, and I add 0xff and calculate the checksum. Now I can download successfully.

My app code stored in 0xe000 to 0x3ffff, event if the code not occupied full memory, but I should fill 0xff in the left empty memory, and calculate a CRC to store in 0x3fffe and 0x3ffff. I have generate the .srec file I needed, but when I download in flash, the function FLASH_DRV_VerifySection() will return STATUS_ERROR becaue FTFx_FSTAT equals to 160, the FTFx_FSTAT_ACCERR_MASK is set, the address is 0x3f020. I check the reference manual, as below.

If the parameter check fails, the FSTAT[ACCERR] (access error) flag is set.

ACCERR reports invalid instruction codes and out-of bounds addresses.

Is the address 0x3f020 protected address? I didn't protect this area. just protect 0x10000000 to 0x1000ffff for eeprom.

Waiting for your reply.

Best regards,

Sarah

Hi Sarah,

Can I see the parameters which you are using for the function FLASH_DRV_VerifySection(?,?,?,?)?

Thank you.

Best regards,

Diana

Hi Diana,

I try to set the different values for the third parameter, and the verify function will return error at different addresses.

FTFx_WORD_SIZE---0x3e020

FTFx_LONGWORD_SIZE---0x3f020

FTFx_PHRASE_SIZE---0x3f820

FTFx_DPHRASE_SIZE---0x3fc20

Obviously, the third parameter effect the result. Could you please explain how should I set this parameter?

Based on my origianl setting, I try to program the flash at 0x3f000, length is 16Bytes, it's OK, but it's NOT OK at 0x3f010.

And I check the register FSEC, SEC is 10b, MCU security status is unsecure.

So I considered the reference factors, and do above test, but still can't find the solution. Could you please help me analyze this problem?

Best regards,

Sarah

Hi Sarah,

At first, I would like to mention that the driver uses flash commands which requirements are described in the RM rev 11.

1. I would like to start with program flash. The FLASH_DRV_Program function uses Program phrase command (36.5.11.4 Program Phrase command). The requirement is that the flash address Must be 64-bit aligned (Flash address [2:0] = 000)

That is why this address 0x3f000 works for you.

2. The FLASH_DRV_VerifySection uses Read 1s Section command (Table 36-34. Read 1s Section command FCCOB requirements). This command requires:

- 64-bit aligned (Flash address [2:0] = 000) for non-interleaved flash.

- number of double phrases which is third parameter of the FLASH_DRV_VerifySection() function. We know that the one phrase is 8B and the double phrase is 16B.

We can define:

#define FTFx_DPHRASE_SIZE 0x0010U

For example,

Let's say that I want to verify memory from the address from 0x0000 to 0x40000

address = 0x0000

size = 0x40000 => 256kB

number of double phrases = 0x40000/0x0010 => 0x4000 => 16

FLASH_DRV_VerifySection(&pSSDConfig, address, size / FTFx_DPHRASE_SIZE, 1u);

---------------------------------------------------------------------------------------------------------------------------------

If you want to verify flash at 0x3f000, length is 16Bytes.

The parameters:

address = 0x3f000

size = 0x0010 => 16B

number of double phrases = 0x0010/0x0010 => 1

I hope it helps.

Best regards,

Diana

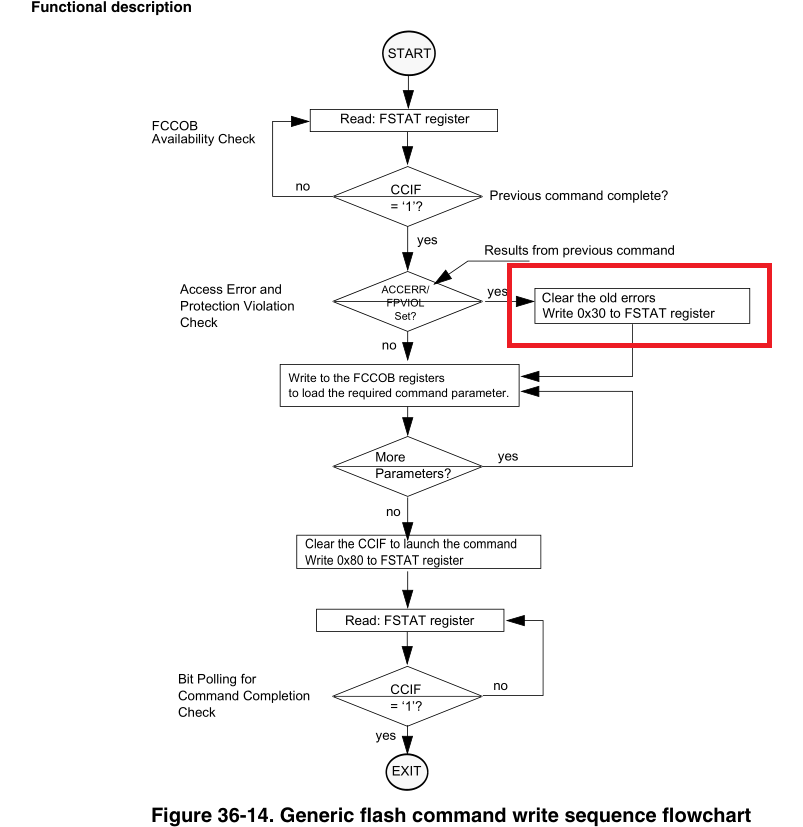

I read the reference manual, and find that if there is access error or protection violation, the FSTAT register should be set as 0x30 to clear the error for next command, check the red rectangle in the attachment.

In the code, it clears the above errors before new command, but there is another condition (STATUS_SUCCESS == ret) before clear.

So if last command contains errors, it will not execute the next command. And this is not keeping with the flowchat.

{

/* Check CCIF to verify the previous command is completed */

if (0U == (FTFx_FSTAT & FTFx_FSTAT_CCIF_MASK))

{

ret = STATUS_BUSY;

}

else

{

/* Clear RDCOLERR & ACCERR & FPVIOL flag in flash status register. Write 1 to clear */

CLEAR_FTFx_FSTAT_ERROR_BITS;

#if (FEATURE_FLS_DF_BLOCK_WRITE_UNIT_SIZE == FTFx_PHRASE_SIZE)

FTFx_FCCOB0 = FTFx_PROGRAM_PHRASE;

#else

FTFx_FCCOB0 = FTFx_PROGRAM_LONGWORD;

#endif

FTFx_FCCOB1 = GET_BIT_16_23(dest);

FTFx_FCCOB2 = GET_BIT_8_15(dest);

FTFx_FCCOB3 = GET_BIT_0_7(dest);

{

temp = FTFx_BASE + i + 0x08U;

*(uint8_t *)(temp) = pData[i];

}

ret = FLASH_DRV_CommandSequence(pSSDConfig);

dest += FEATURE_FLS_PF_BLOCK_WRITE_UNIT_SIZE;

/* Update size for next iteration */

size -= FEATURE_FLS_PF_BLOCK_WRITE_UNIT_SIZE;

/* Increment the source address by 1 */

pData += FEATURE_FLS_PF_BLOCK_WRITE_UNIT_SIZE;

}

}