- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

ECC FlexCAN Fault Injection Sequence & RTD Examples

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi There,

I am a little confused about the FlexCAN ECC fault-injection RTD driver sequence in particular:

1) Can you give me some examples ? I don't find anything in S32 studio nor in RTD examples nor in NXP community...

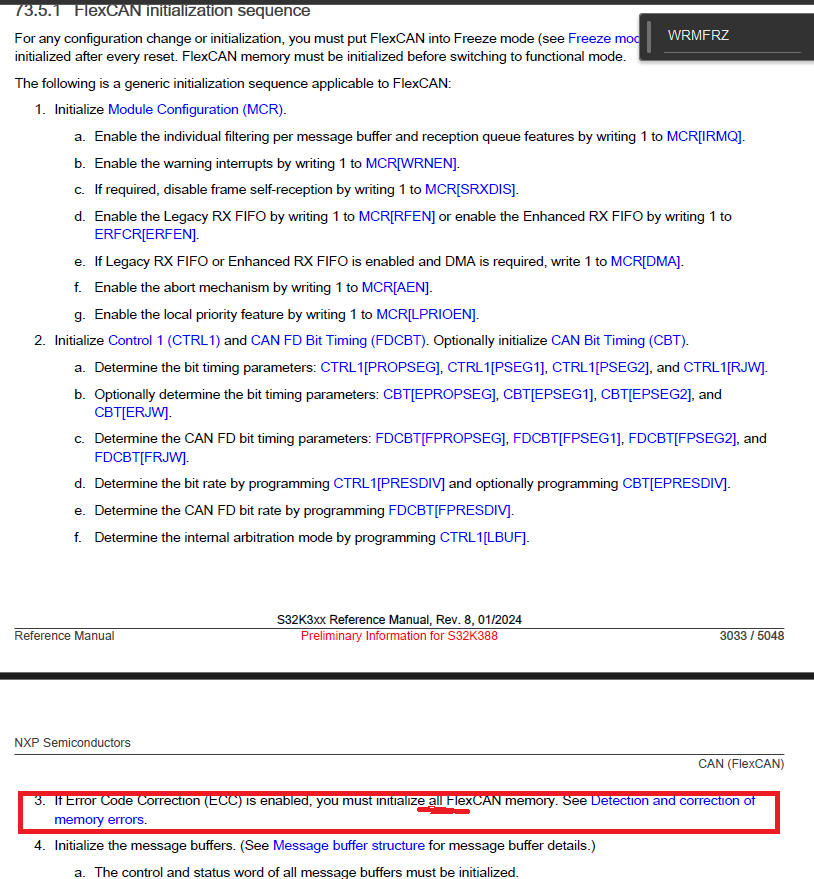

2) Anywhere another question is related to Reference manual rev8 page 2976

a) the initialization of all flexcan memory address range and register (red-1) is done by FlexCAN_ip_Init() or must be done by user ?... I don't find any initialization in RTD and (red-2) I don't understand it, this bit should be set or reset, and what is the meaning of the statement?

3) is it necessary to call FlexCAN_Init() before fault injection process ?. It seems it is not necessary (and this would be a good thing for my software structure)

4) I suppose that a correct sequence starts with :

FlexCAN_Ip_SetMemErrorDetection(INST_FLEXCAN_0,true);

FlexCAN_Ip_SetMemErrorDetectionInt(INST_FLEXCAN_0, FLEXCAN_ALL_ECC_ERROR, true);

FlexCAN_Ip_SetMemErrorInjection();

... ??...

Can you give me some help ?

Best Regards

Fabio

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

1) unfortunately I am not aware of such example to test FlexCAN ECC

2) FlexCAN_Ip_Init is doing memory init calling FlexCAN_ClearRAM, but it does not seem it clears all location stated in the RM, as far as I got the code

3) before ECC is tested a RAM must be initialized and it would be done by FlexCAN_Ip_Init as documentation indicates. FlexCAN_Init is called within FlexCAN_Ip_Init so no need to call it again

4) that sequence seems to be right.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you @PetrS for the answer,

1)regarded point 2) of previous post, I checked too that FlexCAN_ClearRAM, called by FlexCAN_Init() clears a fewer part of the ram indicated in table "FlexCAN Error injection Map" par 73.1.2. p 2975 of RM rev8.

What does it mean that this, do I have to initialize all uninitialized register manually by myself for fault injection?

2) In the project, I previous configured ECC error detection and correction for safety punctual faults management, by calling FlexCAN_Ip_SetMemErrorDetection(..,true) function and and configuring ECC in Normal Mode. But again, I checked that:

So also in runtime detection/correction mechanism, memory(CAN_BASE_ADDR related) from 0x80-0xAD and 0xC20-0x31FF must be initializated.

But FlexCAN_Init() initialize a few part of it.

So does aspect me that runtime Safety Mechanism does not function properly (also without latent faults mechanism (falultInj) developed)?

3) Maybe there are other RTD functions that initializes missing ones ?

Best Regards

Fabio

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

yes, seems RTD is not fully correct with respect of ECC usage. This is disabled by default, i think, so does not bring any issue.

So before you want to enable ECC you need to manually initialize RAM from offsets 0x80-0xAD and 0xC20-0x31FF (or just parts does not covered by FlexCAN_ClearRAM).

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @PetrS

I tried to initialize memory as you suggested in previous post:

You said:

"yes, seems RTD is not fully correct with respect of ECC usage. This is disabled by default, i think, so does not bring any issue.

So before you want to enable ECC you need to manually initialize RAM from offsets 0x80-0xAD and 0xC20-0x31FF (or just parts does not covered by FlexCAN_ClearRAM).:

I have a lot of problems to initialize it outside RTD, because, first you must enter in Freeze mode (and not sure if it is necessary to reset MCR[MDIS] or other stuff ), then clear CAN memory and finally (I think, disable freeze mode (and, maybe disable can....and probabilly some other stuff...)).

But happens to me that sometimes MCU fails to enter in freeze mode and I don't know why .... and other unpredictable behaviours.

Anyway in RM rev8 is reported as Follow (see point 3.):

So ALL flexcan memory is to be initialized only at step 3, after steps 1 and 2 !

FlexCAN_Init() follows exactly these steps and calls correctly FlexCAN_ClearRAM() function. The problem (or bug?) is that function doesen't initialize all 0x80-0xAD and 0xC20-0x31FF (related to CAN_0) memory........... as requested by R. manual.

this is a big problem because:

1) Fault Injection is not possible

2) also ECC runtime management, enabled by FlexCAN_Ip_SetMemErrorDetection() could have some problems, because ECC parity bit are not cleared at init.

So manual says that clear ram need to be performed at a specific initialization step (step 3), but RTD does't clear all memory. (ECC and Fault Inj are required by ASILD)

What is the solution ?

Best regards,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

not sure what to comment more. If ECC is enabled then all memory area specified must be written in Freeze mode to properly set ECC parity bits, otherwise after leaving Freeze module could not work properly depending on error detected.

However if you manually init all needed area, it would work then. FlexCAN_EnterFreezeMode_Privileged/FlexCAN_ExitFreezeMode_Privileged can be used to enter/leave Freeze mode.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

one very last question:

do you know if there is a change to the RTD driver in future releases to clear all ECC ram?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

let me ask SW team.

BR, Petr