- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Can we use LPSPI with the module frequency 48MHz in Run Mode with FIRC?

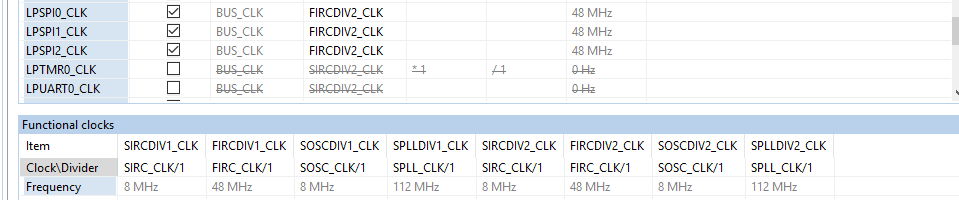

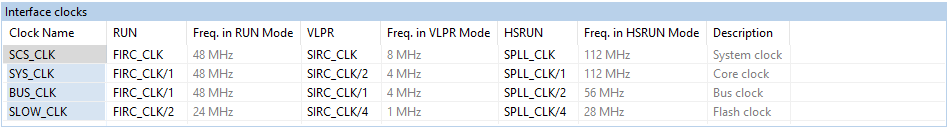

When using FIRC in Run Mode, the frequency of BUS CLK and LPSPI can be set to 48MHz.

Is this setting guaranteed to work?

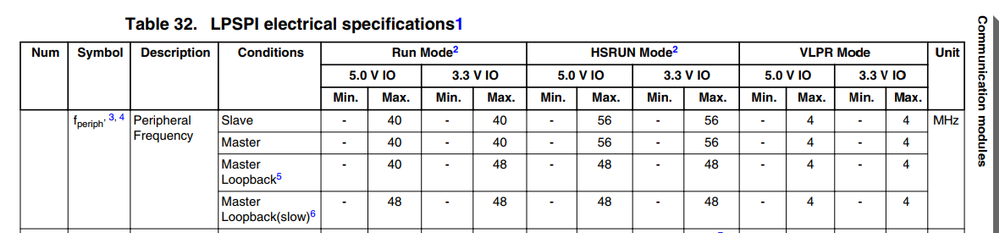

S32K-RM.pdf Rev12.1 P.566 Table 27-8 has a description of "Maximum frequency governed by BUS_CLK", but in the data sheet Rev.11 Table 32. LPSPI electrical specifications, f_periph is Max. 40MHz in Run Mode.

Which description is correct?

If both are correct, why is f_periph limited to 40MHz in Run Mode?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ken3,

Please check the feedback from AE team:

I tested an SDK example “lpspi_transfer_s32k144” with S32K144-EVB, change the BUS_CLK to 48Mhz(If 40 MHz when using PLL as system clock source, S32K-RM, page 560), the LPSPI module is use FIRCDIV2_CLK which is 48Mhz, the program runs normally.

But set BUS CLK to more 40Mhz maybe not an appropriate choice for the LPSPI slave or master communication except loopback according to the S32-DS’s LPSPI electrical specifications (page 52, Table 32), and I think 40Mhz is enough to achieve the max communication baud rate 10Mhz.

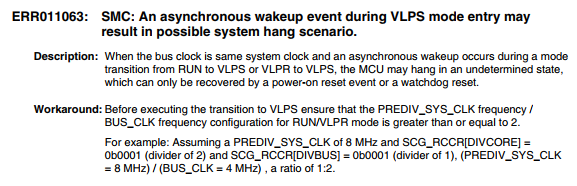

Also if the bus clock is same system clock, an asynchronous wakeup event during VLPS mode entry may result in possible system hang scenario according to ERR011063 in S32K142_0N33V Errata.

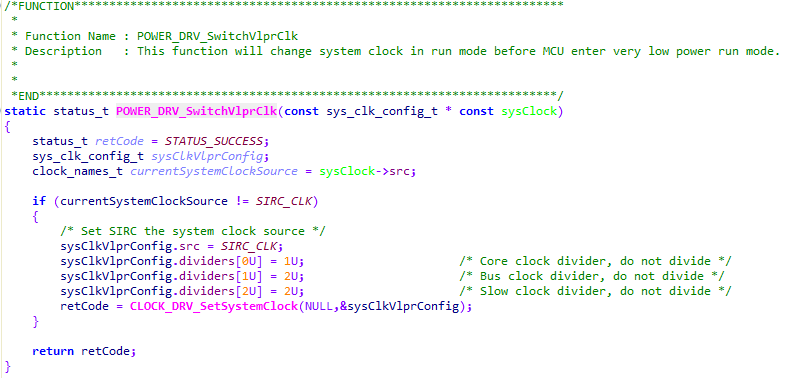

If the users use their code to perform VLPS mode transition must aware of this and take some measures. If use SDK’s pwrMan module, before actually doing the transition the program will switch to a temperate state with the SYS_CLK and BUS_CLK is set to the right value.

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ken3,

Please check the feedback from AE team:

I tested an SDK example “lpspi_transfer_s32k144” with S32K144-EVB, change the BUS_CLK to 48Mhz(If 40 MHz when using PLL as system clock source, S32K-RM, page 560), the LPSPI module is use FIRCDIV2_CLK which is 48Mhz, the program runs normally.

But set BUS CLK to more 40Mhz maybe not an appropriate choice for the LPSPI slave or master communication except loopback according to the S32-DS’s LPSPI electrical specifications (page 52, Table 32), and I think 40Mhz is enough to achieve the max communication baud rate 10Mhz.

Also if the bus clock is same system clock, an asynchronous wakeup event during VLPS mode entry may result in possible system hang scenario according to ERR011063 in S32K142_0N33V Errata.

If the users use their code to perform VLPS mode transition must aware of this and take some measures. If use SDK’s pwrMan module, before actually doing the transition the program will switch to a temperate state with the SYS_CLK and BUS_CLK is set to the right value.

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------