- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Hi,

Pre-Information:

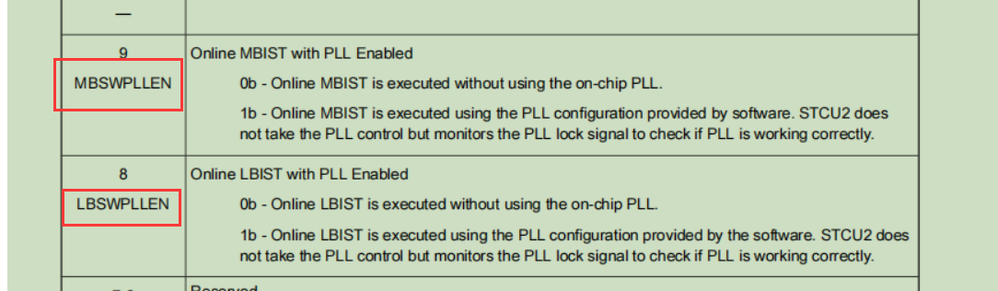

In the "safety->STCU2" section of S32K3XXRM, there is a register related to PLL monitoring located at STCU2->RUNSW. According to the description, when our clock configuration uses PLL, we need to enable these two fields.

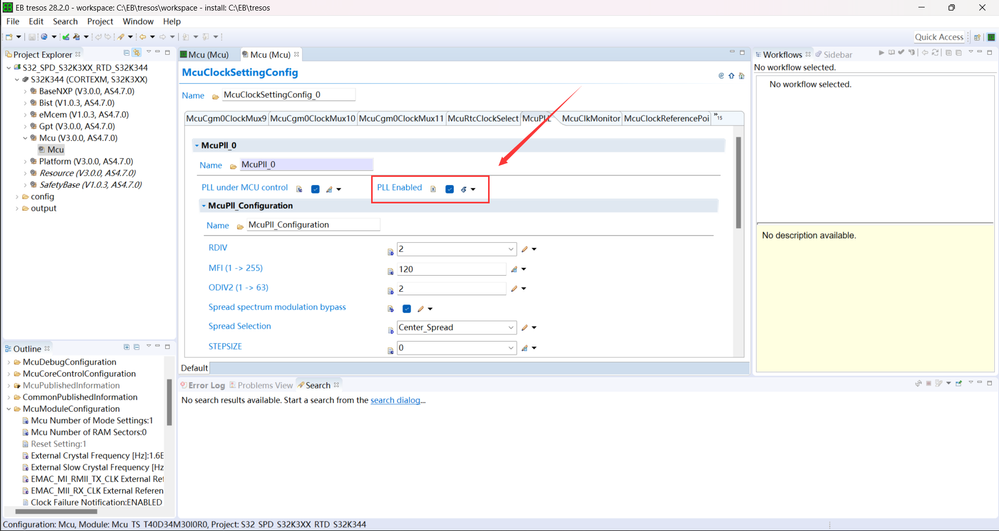

In the demo provided by S32K3 Safety Peripheral Drivers version 1.0.3 Design : Product Download : Files (flexnetoperations.com), PLL is enabled.

Based on the above information, these two bits should be set to 1 in the STCU2->RUNSW register in the demo.

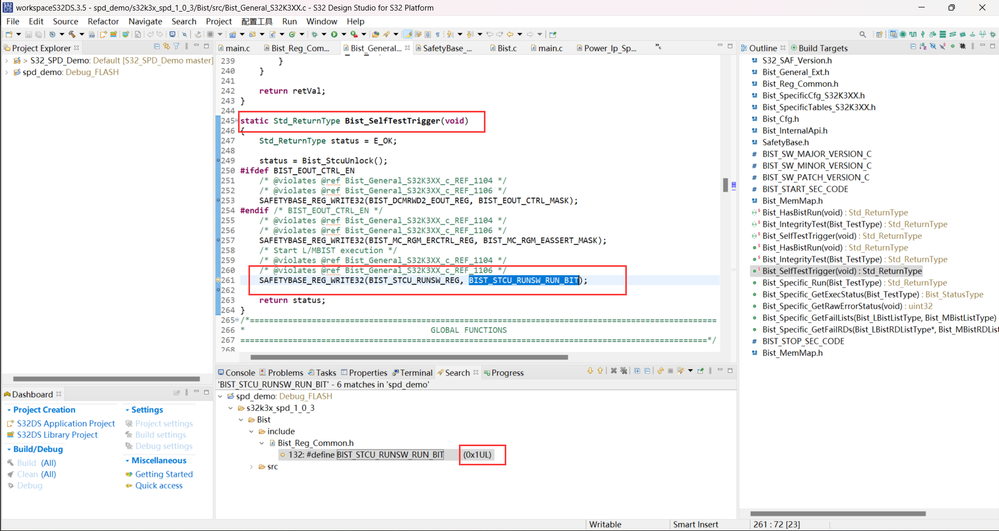

And in the main.c file of the provided demo, the place where this register is set is in BIST_RUN()->Bist_Specific_Run()->Bist_SelfTestTrigger()->SAFETYBASE_REG_WRITE32(BIST_STCU_RUNSW_REG, BIST_STCU_RUNSW_RUN_BIT);

However, in the case where PLL is enabled in the clock configuration, the library driver provided by SPD does not set these two bits to 1.

1. Is this a design flaw or do users need to manually modify certain code?

2. If it's a design flaw, how should we fix it?

已解决! 转到解答。

Hello,

I was talking to SW team as well as the HW validation team.

It look its weird combination of some PowerPC and ARM remnant in documentation.

They confirmed me that the bits are not set by the driver and it is not needed.

As the result the bits are on other ARM devices which carry STCU2 module marked as reserved.

I expect that during reset state these bits are set from factory DCF records so therefore you don't need to set them.

Anyway, Program STCU2 as per NXP recommended in SAF.

And since it has pass the tests, it is valid and PLL is used as test clock.

Best regards,

Peter

Hello,

However, in the case where PLL is enabled in the clock configuration, the library driver provided by SPD does not set these two bits to 1.

1. Is this a design flaw or do users need to manually modify certain code?

2. If it's a design flaw, how should we fix it?

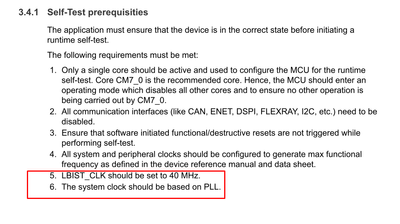

As the only validated configuration is with PLL:

I assume these bits are set in BIST precondition sequence of driver.

Otherwise you will get a STCU2 watchdog error in STCU2_ERR register as the execution wont finish in time with slower IRC clock.

Are you able to execute the test successfully?

On top of that you wont be able to debug the RUNSW register, as soon as you write 1 to run, you will loose access to the micro.

But I am not deeply familiar with SAF driver, so I cant speak for the SW team. That would require to rise ticket at NXP.com

Best regards,

Peter

Hello,

1. I was able to pass the test successfully using BIST_RUN() provided by the SPD library, even though BIST_RUN() does not set these two bits to 1.

2. Can you tell me how to ask this question to the SW team on NXP.com? I haven't found the corresponding method.

Hello,

I was talking to SW team as well as the HW validation team.

It look its weird combination of some PowerPC and ARM remnant in documentation.

They confirmed me that the bits are not set by the driver and it is not needed.

As the result the bits are on other ARM devices which carry STCU2 module marked as reserved.

I expect that during reset state these bits are set from factory DCF records so therefore you don't need to set them.

Anyway, Program STCU2 as per NXP recommended in SAF.

And since it has pass the tests, it is valid and PLL is used as test clock.

Best regards,

Peter

Hello,

Based on the above information, these two bits should be set to 1 in the STCU2->RUNSW register in the demo.

This depends on if you are going to execute the BIST with PLL as the clock. If not, then those bits can be left with 0.

Setting PLL in MCU mode control set the clock to system. It does not mean the BIST will run from PLL.

That is set in BIST precondition.

So first clear out if you want to run BIST with PLL as its clock, then set the proper BIST precondition for it (this should be documented in SAF /SPD docs) and run the test.

Best regards,

Peter

Hello,thanks for your reply.

Setting PLL in MCU mode control set the clock to system. It does not mean the BIST will run from PLL.

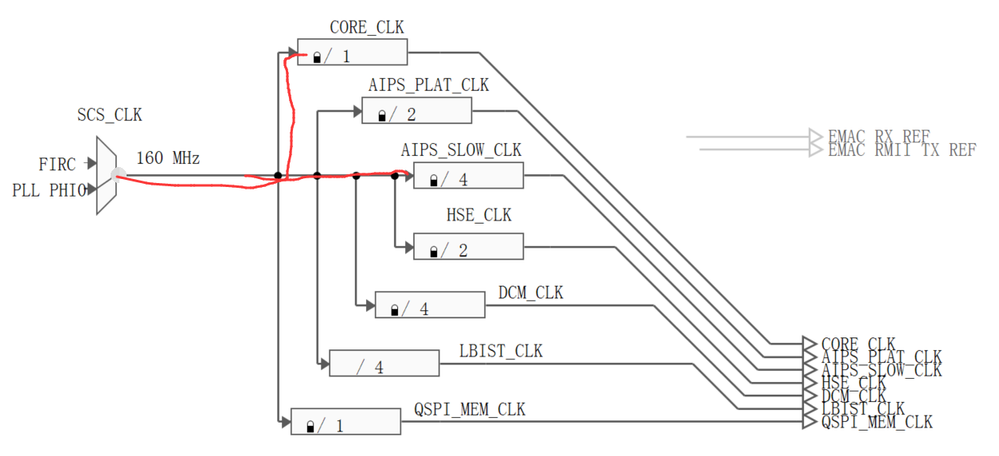

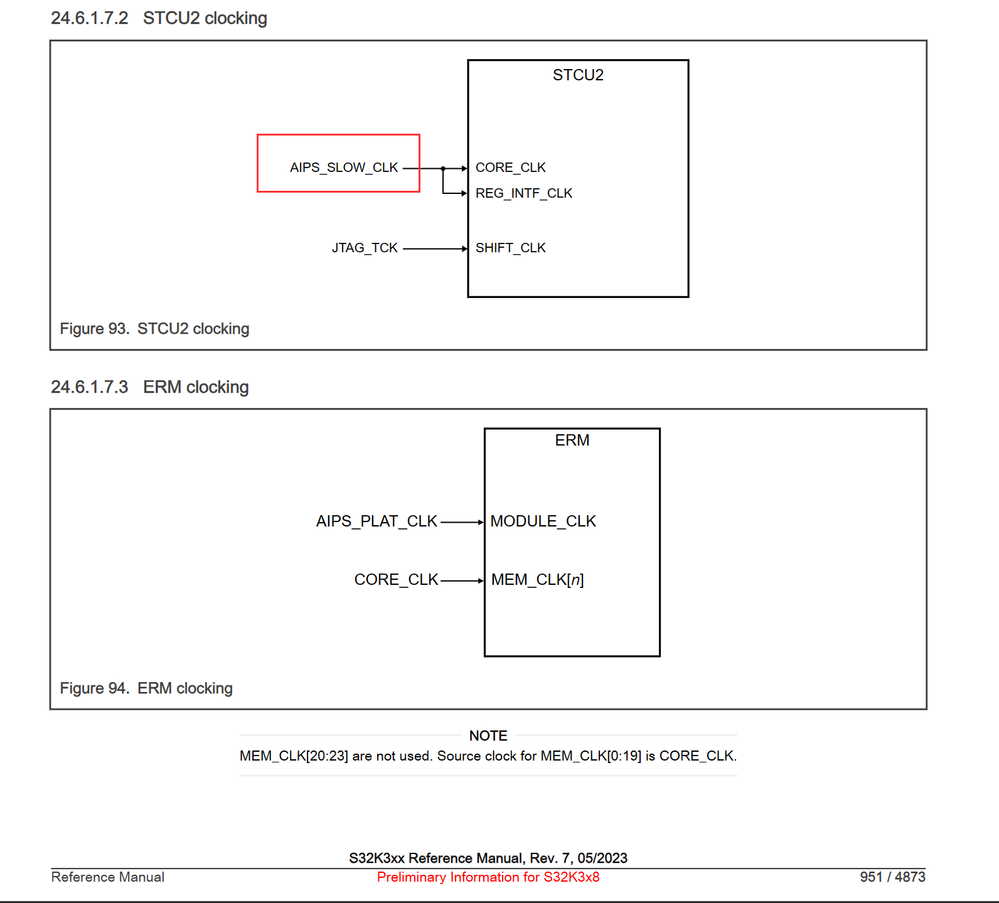

However, according to the two images below, for S32K344, if the clock signal generated by PLL is used as the source of the system clock, then STCU2 will also run from the PLL.