- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Software Forums

- :

- S32 SDK

- :

- Re: S32K146 LPI2C interrupt time is variable

S32K146 LPI2C interrupt time is variable

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K146 LPI2C interrupt time is variable

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

I am using S32K146' LPI2C to connect with fxls8962 to get the accelerator data. the baud rate is 400kbps, with interrupt not DMA. Now I put the task in a 40ms task.c which runs every 40ms. I can read the data from fxls8962 with INT1 pin's interrupt.

But if I use oscilloscope to watch the INT1 pin, the length of each INT1 is not the same, in fact it is variable from about 200us to as long as 10ms. And if I read 1byte each time or read 6 byte each time, the length of INT1 from oscilloscope is nearly the same. in my understanding the I2C should keeps at most 300us each time. I do not know why it can keep as long as 10ms.

And if I use oscilloscope to watch the SCL or SDA pin, each interrupt the length time is the same, about 300us, just the same as expectation.

So I think maybe there is some problem during process the FIFO? But I just use the NXP's LPi2c driver, never change it. I do not know why. Thank you.

Yanpo,li

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yanpo, li,

The behavior with PORT_INT_LOGIC_ONE / PORT_INT_FALLING_EDGE makes sense.

You can make it more robust using the digital filter on the pin (RM rev.11, Section 12.7.5 Digital filter).

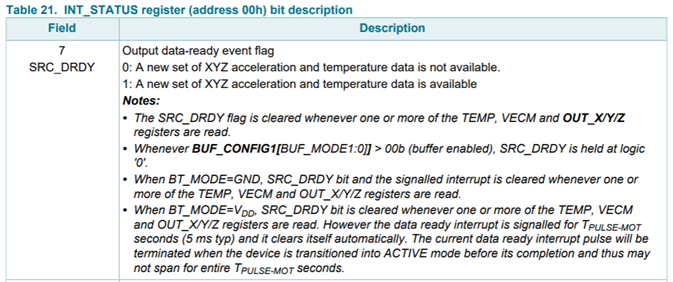

I'm not an expert on the fxls8962 chip, but as far as I know, the INT1 signal is asserted until the data are read (BT_MODE = GND).

The INT1 signal and the 40ms task are not synchronized.

So, I think that we can expect that the INT1 signal is asserted for 10ms - it is waiting for the task and it is cleared when the task is reading the data.

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

1. from I2C signal to INT1 signal, there is about 90us delay. Then INT1 keeps HIGH from 200us to 10ms, then turn to Low.

2. BT_MODE = GND.

3. insert set and clear portE6 in the interrupt handler function(begin and end). it is very strange that during each interrupt the pulse number of portE6 is not the same. In my view, there should be only one pulse of portE6 during each interrupt handler. that is set it and clear it. However, I find in fact there is different number of pulses( portE6) in each interrupt handler, there total time varies from 200us to 10ms. the same as the INT1, And during the 200us to 10ms time there are many pulses, each pulse is about 1.3us. I do not know why there are so many pulses in each interrupt handler? for this means in each interrupt handler there are several times INT1 handler again?

This problem I have solved. for my program's interrupt level is set as "PORT_INT_LOGIC_ONE" , when I change it to "PORT_INT_FALLING_EDGE" , there is only once interrupt every 40ms just as expected. And the others task can be executed normally.

However, I can not understand the keep time of INT1 is still just as before. its keep time varies from 200us to 10ms.

4. what the interrupt handler do is set the flag to 1, and in the 40ms task, when check the flag ==1 read the fxls8962 data. if not set, just pass it.

Thank you for your time.

Yanpo, li

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

yes, it is configured as data ready interrupt pin, to tell the master the data is ready every 40ms. the problem is what I expect is the INT1 pin should keep for the same time each interrupt, however, what I got from the oscilloscope is the INT1 PIN's keeping time is increasing from 200us to 10ms , then back to 200us and increase to 10ms again. That means the LPI2C reading task's keeping time is varying, not fixed. And I hope the LPI2C reading task's keeping time is very short, nearly 300us.

Besides, I use the following to get the fxls8962's data. Thank you.

Status = LPI2C_DRV_MasterSendDataBlocking(INST_LPI2C1, &TxBuffer,TRANSFER_SIZE_BYTE , true,GSM_SPI_TIMEOUT);

if (STATUS_SUCCESS != Status)

{

return G_SENSOR_ERROR_WRITE;

}

/* Request data from the bus slave */

// DISABLE_INTERRUPTS();//must be blocked

Status = LPI2C_DRV_MasterReceiveDataBlocking(INST_LPI2C1, pBuffer, len, true,GSM_SPI_TIMEOUT);// len =6 byte or 1 byte is the same result

// ENABLE_INTERRUPTS();

if (STATUS_SUCCESS != Status)

{

return G_SENSOR_ERROR_READ;

}

or, the configuration of fxls8962 is not correct? But I can read the data by I2C. my configuration is as the following.

registerwritelist_t cFxls8962ConfigMotionDetect[] = {

{FXLS8962_SENS_CONFIG3, FXLS8962_SENS_CONFIG3_WAKE_ODR_100HZ, FXLS8962_SENS_CONFIG3_WAKE_ODR_MASK},

{FXLS8962_SENS_CONFIG4, FXLS8962_SENS_CONFIG4_DRDY_PUL_DIS, FXLS8962_SENS_CONFIG4_DRDY_PUL_MASK},

{FXLS8962_INT_EN, FXLS8962_INT_EN_DRDY_EN_EN, FXLS8962_INT_EN_DRDY_EN_MASK},

/* {FXLS8962_INT_EN, FXLS8962_INT_EN_SDCD_OT_EN_EN, FXLS8962_INT_EN_SDCD_OT_EN_MASK},*/

{FXLS8962_ORIENT_CONFIG, FXLS8962_ORIENT_CONFIG_ORIENT_ENABLE_DIS, FXLS8962_ORIENT_CONFIG_ORIENT_ENABLE_MASK},

{FXLS8962_SDCD_CONFIG1,

FXLS8962_SDCD_CONFIG1_X_OT_EN_EN | FXLS8962_SDCD_CONFIG1_Y_OT_EN_DIS | FXLS8962_SDCD_CONFIG1_Z_OT_EN_DIS,

FXLS8962_SDCD_CONFIG1_X_OT_EN_MASK | FXLS8962_SDCD_CONFIG1_Y_OT_EN_MASK | FXLS8962_SDCD_CONFIG1_Z_OT_EN_MASK},

{FXLS8962_SDCD_CONFIG2, FXLS8962_SDCD_CONFIG2_SDCD_EN_DIS | FXLS8962_SDCD_CONFIG2_REF_UPDM_FIXED_VAL |

FXLS8962_SDCD_CONFIG2_OT_DBCTM_CLEARED | FXLS8962_SDCD_CONFIG2_WT_DBCTM_CLEARED,

FXLS8962_SDCD_CONFIG2_SDCD_EN_MASK | FXLS8962_SDCD_CONFIG2_REF_UPDM_MASK | FXLS8962_SDCD_CONFIG2_OT_DBCTM_MASK |

FXLS8962_SDCD_CONFIG2_WT_DBCTM_MASK},

{FXLS8962_SDCD_WT_DBCNT, MD_SDCD_WT_DBCNT, 0},

{FXLS8962_SDCD_LTHS_LSB, SDCD_LTHS_LSB, 0},

{FXLS8962_SDCD_LTHS_MSB, SDCD_LTHS_MSB, 0},

{FXLS8962_SDCD_UTHS_LSB, SDCD_UTHS_LSB, 0},

{FXLS8962_SDCD_UTHS_MSB, SDCD_UTHS_MSB, 0}

};

Yanpo, li

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yanpo, li,

I'm not familiar with the fxls8962 device.

But if I'm not mistaken, the INT1 signal remains asserted until the data are read (BT_MODE = GND).

If BT_MODE = VDD, the signal should be deasserted in about 5ms.

I understand that you want to read the data as soon as the INT1 signal is asserted, but there is a delay between the INT1 assertion and the I2C bus transfer.

Can you measure both the INT1 signal and the I2C bus at the same time to determine the delay?

Do you use a PORT interrupt on an falling edge to detect the INT1 signal?

Once the signal is detected, what exactly is the application doing?

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi yli23@lear.com,

I have difficulties to understand.

I see that the pin is configurable, so, what exactly is the function of the INT1 pin, is the INT1 pin driven by fxls8962?

Is the INT1 a host request signal (HREQ) for the LPI2C master?

Thanks,

BR, Daniel