- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 软件论坛

- :

- S32 Design Studio

- :

- S32K144:SPI Transfer

S32K144:SPI Transfer

S32K144:SPI Transfer

Hello all,

I tried to use SPI transfer with CS as GPIO. I'm performing following steps.

1. Making the CS LOW

2. Pushing to data in the FIFO

3. Making the CS HIGH

I'm able to transfer the data but my CS goit HIGH (Step 3) Far ahead of the transfer.

CS_LOW;

LPSPI0->TDR = LPSPI_TDR_DATA(n) ;

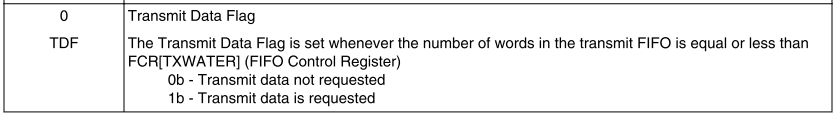

while((LPSPI0->SR & LPSPI_SR_TDF_MASK)>>LPSPI_SR_TDF_SHIFT==0) {}

CS_HIGH;

Kindly help in this regard,

Raju

/* SPI FLASH Sequence for 1 bytes is OK */

LPSPI1->TCR = ((LPSPI1->TCR) | (LPSPI_TCR_BYSW_MASK));

LPSPI1->TCR = ((LPSPI1->TCR) & (~LPSPI_TCR_BYSW_MASK));

LPSPI1->FCR = 0x00000003; /* RXWATER=0 TXWATER=3 */

lpspi_tmp = ((LPSPI1->TCR) & (~LPSPI_TCR_FRAMESZ_MASK));

LPSPI1->TCR = (lpspi_tmp | (7U & LPSPI_TCR_FRAMESZ_MASK));

PINS_DRV_ClearPins(PTB, 1 << 17); /* Software Control PCS3 : SET PCS3 LOW */

while (((LPSPI1->SR & LPSPI_SR_TDF_MASK) >> LPSPI_SR_TDF_SHIFT) == 0);

LPSPI1->TDR = ( uint32_t ) (*txdata_p++); /* for 1 bytes */

LPSPI1->TCR = ((LPSPI1->TCR) | (LPSPI_TCR_TXMSK_MASK)); /* Start Transmit and Hardware Auto Clear */

LPSPI1->TCR = ((LPSPI1->TCR) & (~LPSPI_TCR_RXMSK_MASK));

LPSPI1->SR |= LPSPI_SR_TDF_MASK; /* Clear TDF flag */

while (((LPSPI1->SR & LPSPI_SR_RDF_MASK) >> LPSPI_SR_RDF_SHIFT) == 0);

lpspi_tmp = LPSPI1->RDR;

*rxdata_p++ = ( uint8_t ) (lpspi_tmp >> 0);

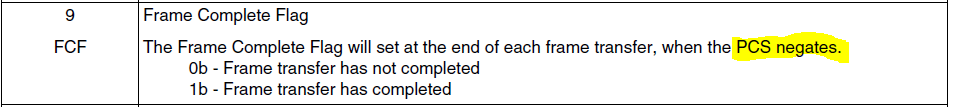

while (((LPSPI1->SR & LPSPI_SR_FCF_MASK) >> LPSPI_SR_FCF_SHIFT) == 0);

LPSPI1->SR |= LPSPI_SR_RDF_MASK | LPSPI_SR_FCF_MASK;

LPSPI1->TCR = ((LPSPI1->TCR) & (~LPSPI_TCR_CONTC_MASK));

LPSPI1->CR = 0x00000000; /* Module Disable、Debug Disable */

PINS_DRV_SetPins(PTB, 1 << 17); /* Software Control PCS3 : SET PCS3 High */

Hi,

here's the difference:

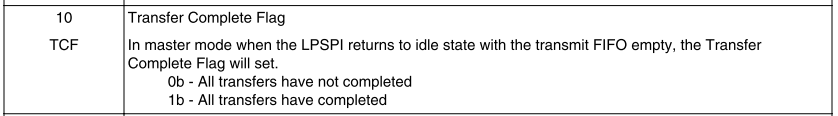

That means you need to wait for TCF flag, not for TDF.

Regards,

Lukas

Hi Lukas,

Thanks for the response.

I tried waitng till

while((LPSPI0->SR & LPSPI_SR_TCF_MASK)>>LPSPI_SR_TCF_SHIFT==0) {}

Even I tried to wait for the FCF flag to set. I don't see any change considering by frame length as 7+1 bits

but, stranges the TCF, FCF, WCF flag will set immeadiately after writing the data into the tranmit buffer though theCS still holds the LOW.

Kindly help in this regard,

Raju

That's a good point, I did quick test and I can see that too. TCF flag is obviously set when data are transferred to shift register and physical transmission is not considered.

But in fact, the description is correct:

"In master mode when the LPSPI returns to idle state with the transmit FIFO empty, the Transfer Complete Flag will set."

In other words, TCF is set immediately when FIFO is empty.

As a workaround, you can use delay loop instead for waiting for flag. Just calculate required time for your SPI frequency.

Regards,

Lukas