- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- S12ZVC interrupt priority

S12ZVC interrupt priority

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

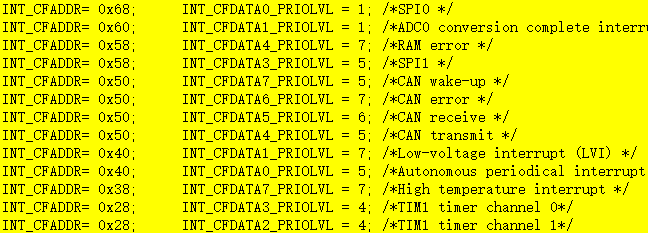

I see the S12ZVC datasheet:two registers INT_CFADDR and INT_CFDATA0-7.There is something I donot understand.

Is it means S12ZVC can deal at most 8 interrupts at a point. By configure the INT_CFDATA0-7 ,am I able to deal an interrupt at first ,whose interrupt priority is lower. when two interrupts occuered. IS there any demo code to describe it .Thank you!

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For example, S12ZVML12_Hall_BLDC demo uses the below function:

/*****************************************************************************

*

* Function: void InitINT(void)

*

* Description: Interrupt priorities configuration

*

*****************************************************************************/

void InitINT(void)

{

// set ADC 0 done ISR (0x184) priority to 6

// 0x184 / 4 = 0x61 => reg. 0x60, offset 1

INT_CFADDR = 0x60;

INT_CFDATA1 = 6;

// set ADC 0 error ISR (0x18C) priority to 2

// 0x18C / 4 = 0x63 => reg. 0x60, offset 3

INT_CFADDR = 0x60;

INT_CFDATA3 = 2;

// TIM ch1 input capture ISR (0x1C8) priority set to 5

// 0x1C8 / 4 = 0x72 => reg. value = 0x70 + offset 2

INT_CFADDR = 0x70;

INT_CFDATA2 = 5;

// TIM ch3 output compare ISR (0x1C0) priority set to 4

// 0x1C0 / 4 = 0x70 => reg. value = 0x70 + offset 0

INT_CFADDR = 0x70;

INT_CFDATA0 = 4;

}Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There is the paging mechanism. You can configure all 128 interrupts priority with only 9 registers.

For instance, if you want to have two interrupts with different priority, let’s say:

CAN receive (Vector base + 0x154) and Port L (Vector base + 0x0C0)

Then for CAN receive interrupt:

Vector address/vector size = 0x154 / 4 = 0x55. We use only bit [7..4] for INT_CFADDR configuration. In this case, it is 0x50.

INT_CFADDR = 0x50;

The 3 LSB of 0x55 are 0b101 = 5, therefore for priority configuration of this interrupt use data register 5 and load it with priority you need.

INT_CFDATA5_PRIOLVL = 0x01; /*Priority level of CAN receive */

Similarly for Port L

INT_CFADDR = 0x30;

INT_CFDATA0_PRIOLVL = 0x02; /* Priority level of Port L */

The higher PRIOLVL number means the higher interrupt priority. With PRIOLVL = 0 the corresponding interrupt is disabled.

If more than one interrupt request is configured to the same interrupt priority level the interrupt request with the higher vector address wins.

You may look at S12Z CPU RM for more details about interrupt event principles:

http://www.nxp.com/assets/documents/data/en/reference-manuals/S12ZCPU_RM_V1.pdf

I hope it helps you.

Have a great day,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

As mentioned above,If I need set the CAN and Port L priority at same time.How do I set INT_CFADDR?The CAN is 0x50,Port L is 0x30. I need set INT_CFADDR = (0x50 & 0x30 )?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The INT_CFADDR registers selects 8 vectors out of 128 that are accessible in the 8-byte register window INT_CFDATA0–7. And thus you can't configure CAN and Port L interrupts with just one write to the INT_CFADDR register. You have to configure the interrupts one by one.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

I have set the reg for this,but it still doesn't work.

Is there an example of this part of the project?Tks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For example, S12ZVML12_Hall_BLDC demo uses the below function:

/*****************************************************************************

*

* Function: void InitINT(void)

*

* Description: Interrupt priorities configuration

*

*****************************************************************************/

void InitINT(void)

{

// set ADC 0 done ISR (0x184) priority to 6

// 0x184 / 4 = 0x61 => reg. 0x60, offset 1

INT_CFADDR = 0x60;

INT_CFDATA1 = 6;

// set ADC 0 error ISR (0x18C) priority to 2

// 0x18C / 4 = 0x63 => reg. 0x60, offset 3

INT_CFADDR = 0x60;

INT_CFDATA3 = 2;

// TIM ch1 input capture ISR (0x1C8) priority set to 5

// 0x1C8 / 4 = 0x72 => reg. value = 0x70 + offset 2

INT_CFADDR = 0x70;

INT_CFDATA2 = 5;

// TIM ch3 output compare ISR (0x1C0) priority set to 4

// 0x1C0 / 4 = 0x70 => reg. value = 0x70 + offset 0

INT_CFADDR = 0x70;

INT_CFDATA0 = 4;

}Regards,

Daniel