- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 产品论坛

- :

- S12 / MagniV微控制器

- :

- Re: Question about VCOFRQ setting in S12ZVL

Question about VCOFRQ setting in S12ZVL

Question about VCOFRQ setting in S12ZVL

Hello all,

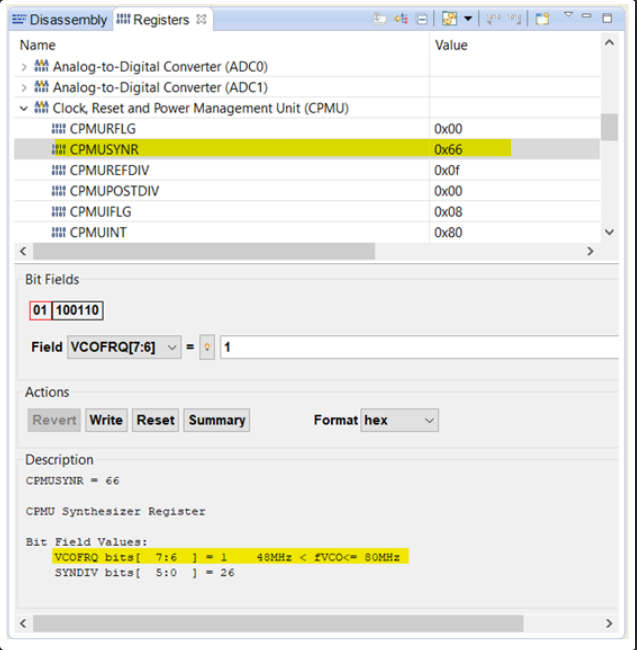

I am currently at the configuration of the fvco of the S12ZVL128. However, I find some difference in the datasheet for VCOFRQ setting. Just want to confirm which is correct.

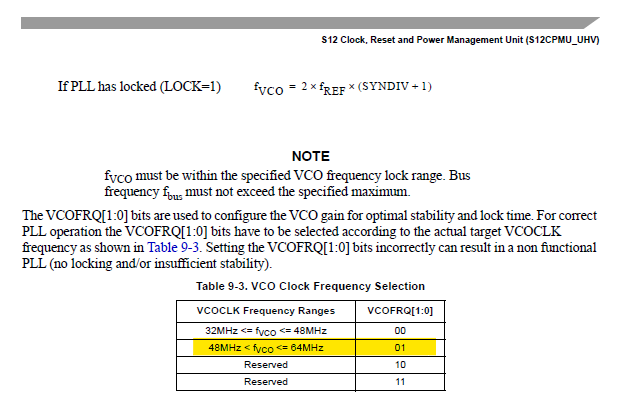

In page. 235, chapter '9.3.2.4 S12CPMU_UHV Synthesizer Register (CPMUSYNR)', I found the following information:

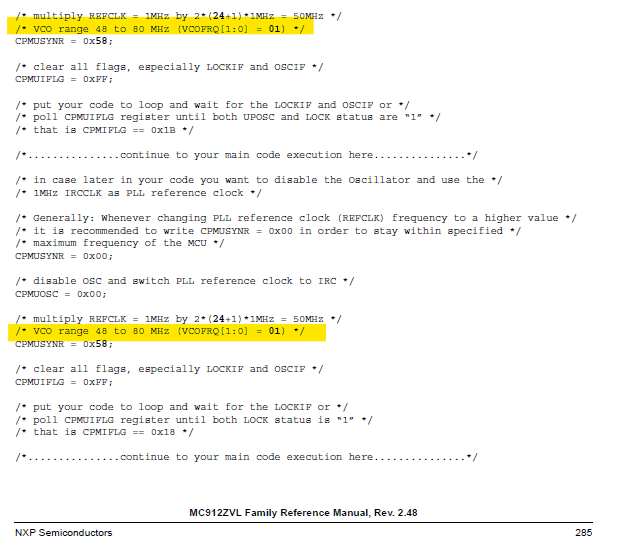

However, in page. 285, for the ‘9.7.3 Application Information for PLL and Oscillator Startup’, it says that range is between 48MHz to 80MHz for VCOFRQ[1:0] = 01:

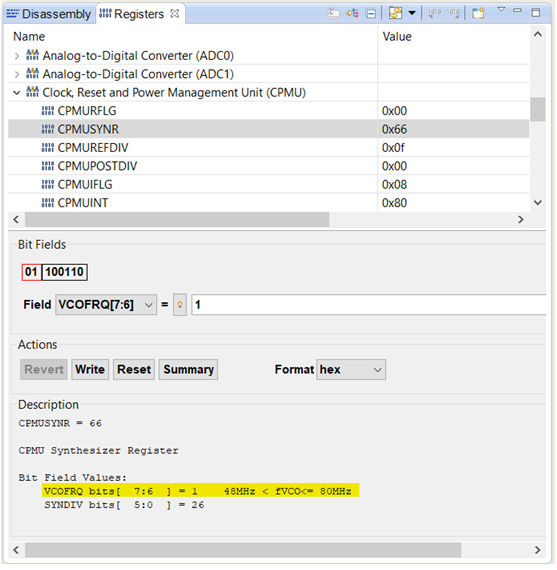

I have also seen the same information in my register window when I was debugging:

Could anyone confirm which is the correct range for the setting?

Thank you,

Junxi

Hello Lama,

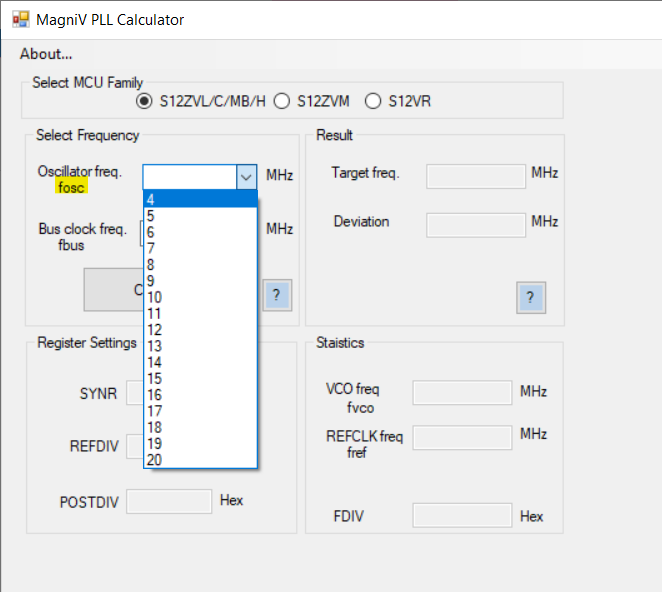

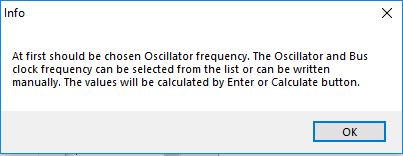

Thank you for sharing the tools. I got one question here for setting it up.

For the Oscillator freq, I am using the internal clock fIRC1M which is 1MHz (OSCE=0), I find I cannot find the correct value here to run the calculation.

Could you please let me know if you have any suggestion?

Thank you,

Junxi

Hello Lama,

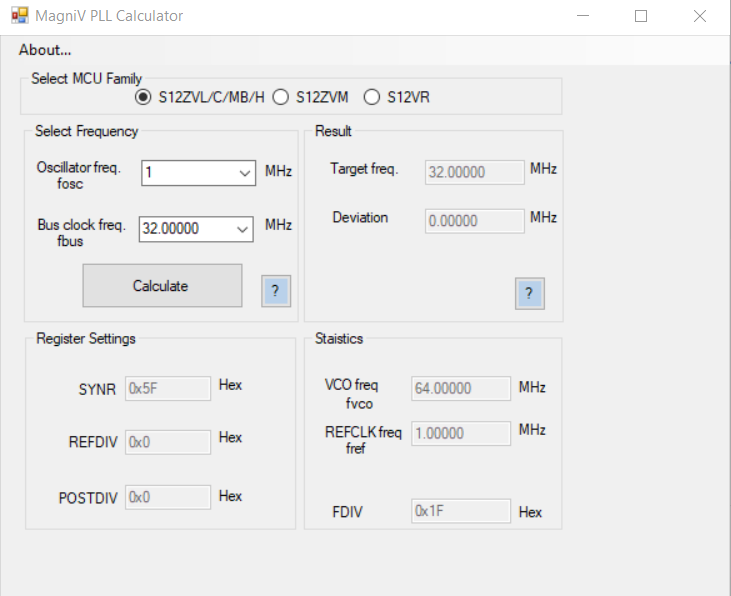

Thank you for the suggestion, I tried it works. I think the maximum I could go is 64MHz for fvco with SYNR 0x5F.

However, what I have seen in my setting is SYNR 0x66, which makes the fvco 78MHz.

If I am using this setting for the fvco, is that means the actual fvco is still 64MHz instead of 78MHz? Or something else?

Is there any easy way to measure the actual fvco or fbus? I think to toggle the I/O pin, which usually take 2 clocks for that to calculate the frequency. Could you please let me know if you have better suggestion?

Thank you,

Junxi

Hi,

The busclk can be measured at ECLK pin (PS3) you clear bit NECLK in ECLKCTL register.

Back to original issue:....

80Mhz mentioned in 9.7.3 Application Information for PLL and Oscillator Startup looks to be a copy/paste typo from a datasheet with the same peripheral but higher frequency possibilities.

You wrote you have CPMUSYNR = 0x66. It is not correct value. The data sheet says to use max fvco=64MHz. If the setup is made by any tool then it must be a bug if it uses fvco= 78MHz for this type of MCU. However, it is possible that this setup will provide you "correct" busclk (I mean the MCU will work) but you will use the MCU out of operating specifications (>32 MHz). I suggest you to change it to defined range.

Your original values:

fref = 1

fvco= 2 * fref * (syndiv+1) ; 0x66=0B01100110 => SYNDIV=0B100110=38

fvco= 78MHz => out of el. specification range

Busclk = fpll/2 = (fvco / (POSTDIV +1)) / 2 = 39MHz => out of el. specification range

Required values for fbus=32MHz:

SYNR = 0x5F

REFDIV =0

POSTDIV=0

Best regards,

Ladislav

Hi,

Max bus clock is 32MHz and you shouldn't violate it. While clocking from PLL, VCO clock is 2x bus clock. Clearly PLL should be able to work reliably way above the 32*2=64MHz margin. Perhaps 80MHz is the real limit for PLL, but CPU and peripherals still are limited to 32MHz and thus 32*2=64MHz VCO.

Edward