- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 製品フォーラム

- :

- S12 / MagniVマイクロコントローラ

- :

- Debugger with watch dog enabled

Debugger with watch dog enabled

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Debugger with watch dog enabled

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have some questions please help

1. Can I work with debugger with watch dog enabled. Currently when working with debugger i am disabling the watch dog timer. But right now i am facing one critical issue where the watch dog reset is happening in production. I want to simulate the same using debugger. any settings i need to make.

2. I found that an unknown message is happening along with two standard identifiers immediately which are not expected and the system reset happens. Is there any possibility that a reset happens if CAN message ids get corrupted. I am using CAN driver interrupts handled by xgate and processed by s12x. Any possibility because of semaphore and etc. please advice.

3. Are there any other kinds of reset apart from watch dog like illegal instruction etc.

Micro i am using is S12X EQ.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi rahul,

1. Debugging when COP watchdog is enabled is quite tricky. You probably cannot use stepping over code because stepping takes longer time than COP timeout. You could set COPCTL_RSBCK bit for Stops the COP and RTI counters whenever the part is in Active BDM mode, but I am afraid that it will not help you so much. For debugging COP reset, you could use indirect methods like LEDs, triggers and trace (trace buffer is not affected by COP reset). For more details, please see "c:\Program Files (x86)\Freescale\CWS12v5.1\Help\PDF\Debugger_HC12.pdf" document.

Are you really sure that it is really COP who invoked MCU reset?

2. We do not know about any direct connection between CAN and reset. So, there must be probably some other issue like illegal address reset, endless loop – COP timeout, low voltage reset,…

Semaphores have to be used for access to shared memory or shared peripheral between CPU and XGATE.

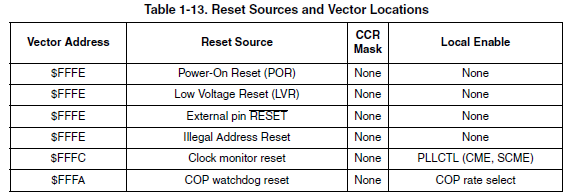

3. Reset sources are described in Table 1-13. Reset Sources and Vector Locations in RM.

I hope it helps you.

Have a great day,

RadekS

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Really it is little bit confusing about the resets. If i take the example of cop watch dog reset if it times out reset will happen then why there is separate interrupt address for COP watchdog reset that is $FFFA why not it is $FFFE. In case if i do not add any function is cop watchdog reset isr. what will happen? Or is the sequence is like first goes to the address $FFFA then goes to $FFFE. please help. Similarly for clock monitor reset and illegal address reset.