- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 製品フォーラム

- :

- S12 / MagniVマイクロコントローラ

- :

- 9S12X assembly instruction clarification

9S12X assembly instruction clarification

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

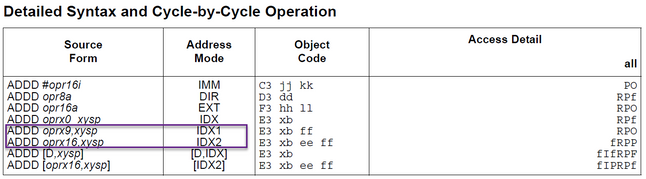

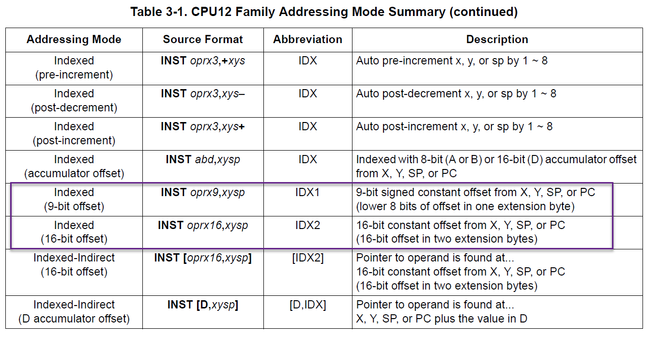

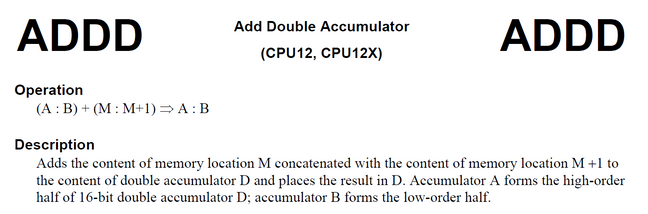

I have some assembly code written for the 9S12X that I am trying to figure out what it does. One instruction is:

ADDD 8,SP I believe that is and instruction to add the contents of Accu D with the contents at stack +8.

Another instruction is :

ADDD (8+2),SP Is that the same as ADDD 10,SP which would be an instruction to add the contents of Accu D with the contents at stack +10?

Regards,

Robert

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Robert,

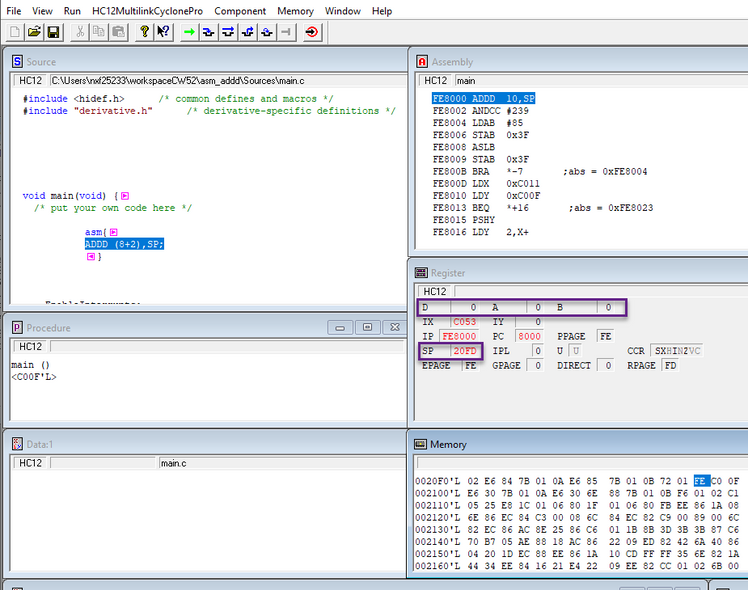

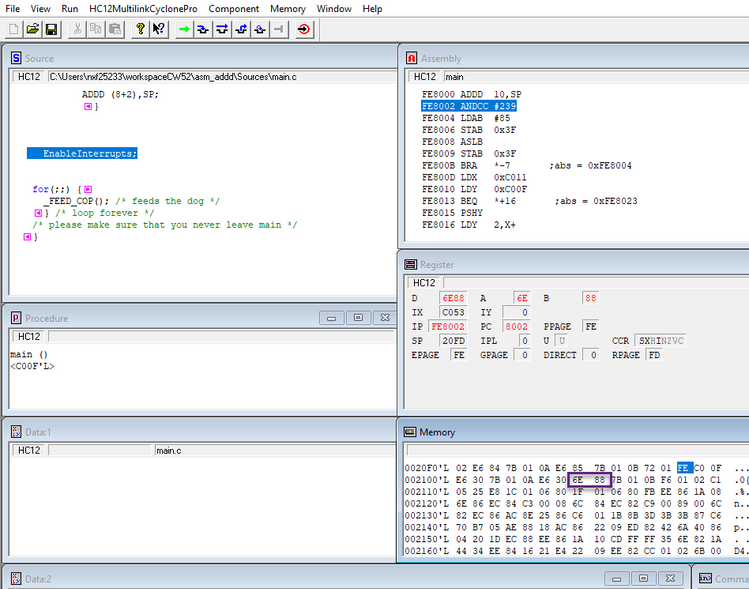

So, (8+2) is an offset to location M which is the SP in this case

M = 0x6E, M+1 = 0x88 which is added to D (A = 0x00, B=0x00).

D = 0x6E88

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Robert,

I'm sorry for the delay.

It is explained in the CPU12X reference manual v01.04.

It concatenates the content of M with the content of M+1 and adds it to the accumulator D.

I believe you can test it in CW 5.2, there is a simulator if you don't have any board.

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Daniel,

Thanks for your response. Yes, I had looked up the ADDD instruction as you posted, and it makes sense when ADDD is followed by a memory location, but I am still confused as to what (8+2),SP means. I'm afraid that any manipulations on the stack confuse me easily.

Regards,

Robert

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Daniel,

Got it, and thanks so much for the lesson in debugging. So it looks like I was correct in my original post where I thought that (8+2),SP could be the same as 10,SP. I wonder why the author would chose to do it that way?

Regards,

Robert

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Robert,

So, (8+2) is an offset to location M which is the SP in this case

M = 0x6E, M+1 = 0x88 which is added to D (A = 0x00, B=0x00).

D = 0x6E88

Regards,

Daniel